# RF-SoP using differential ports for WLAN

Microwave Circuit and System-on-Package Lab. Graduate Inst. of Electronics Engineering, National Taiwan University

## **RF-SoP** approaches

- Replace discrete components with embedded ones for size and area reduction.

- Addition of more functional blocks, such as an antenna or filters to the module.

- Optimize performance by replacing on-chip passives with high-Q passives embedded in package.

# LTCC

- LTCC: low temperature cofire ceramic

- Multi-layer, vias, blind vias, buried resistors

- Passive elements, transmission lines can be placed inside or on surface of LTCC.

- Active elements on surface

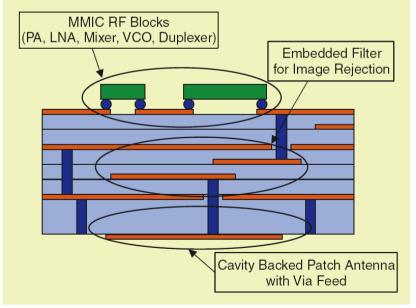

Figure 17. 3D integrated module with CBPA and embedded filter.

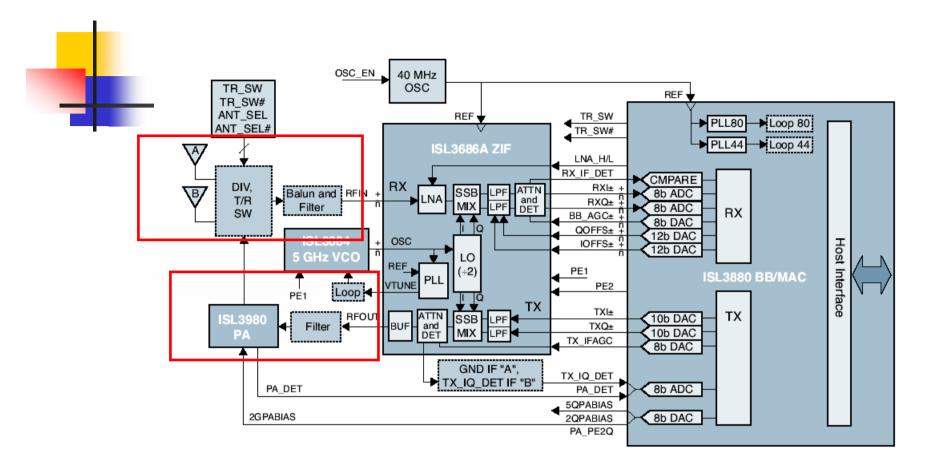

**PRISM GT Block Diagram**

- •Block diagram of Conexant's Prism GT chipset.

- •Balanced input or/and output at chipset.

- •We will work on components inside the red boxes by using differential transmission lines

# Why use balanced circuit?

- Eliminate baluns

- The differential operation could suppress the common mode interference.

- The virtual ground terminal would be compatible with the poor grounding of compact circuit.

- Antennas can also has differential feed.

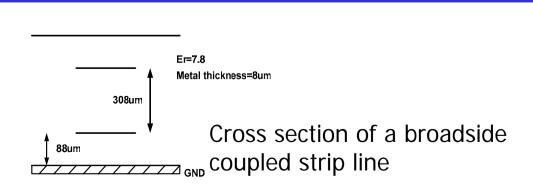

- Broadside coupled stripline or microstrip line are chosen for same area occupation as single ended circuits.

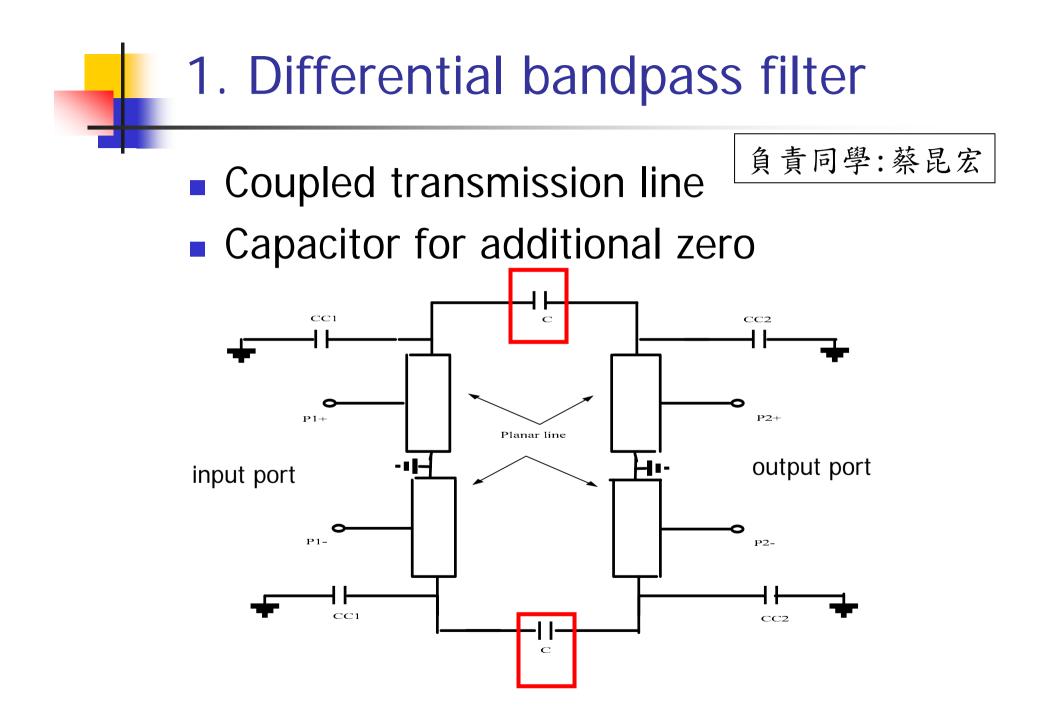

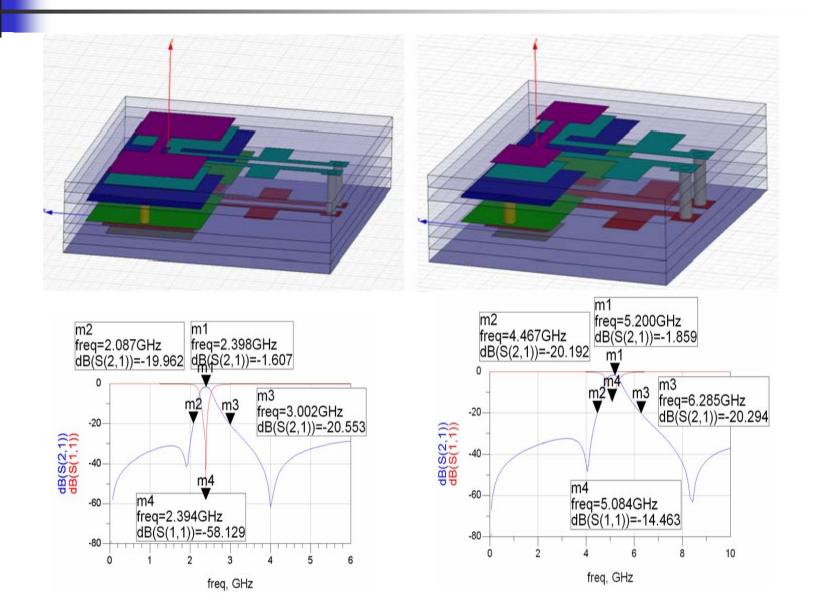

#### 3D layout and simulation results

#### Performance comparison

|                      | S11   | S21    | Attenuation of -<br>20dB   |

|----------------------|-------|--------|----------------------------|

| BPF@2.4GHz           | -28dB | -1.3dB | 1.9GHz <sup>,</sup> 3GHz   |

| BPF+CAP.@2.4<br>GHz  | -58dB | -1.6dB | 2.1GHz <sup>,</sup> 3GHz   |

| BPF@2.4GHz<br>at [1] | -33dB | -2.2dB | 2GHz <sup>,</sup> 3GHz     |

| BPF@5.2GHz           | -29dB | -1.1dB | 4GHz <sup>,</sup> 6.2GHz   |

| BPF+CAP.@5.2<br>GHz  | -14dB | -1.8dB | 4.46GHz,<br>6.2GHz         |

| BPF@5.8GHz<br>at [1] | -13dB | -2.5dB | 4.8GHz <sup>,</sup> 6.8GHz |

[1] Young-Joon Ko, Jae Yeong Park, Jin-Hyung Ryu, Kyeong-Hak Lee, and Jong Uk Bu, "A miniaturized LTCC multi-layered front-end module for dual band WLAN(802.11a/b/g) applications," *IEEE MTT-S Diggest*, pp.536-566, June 2004.

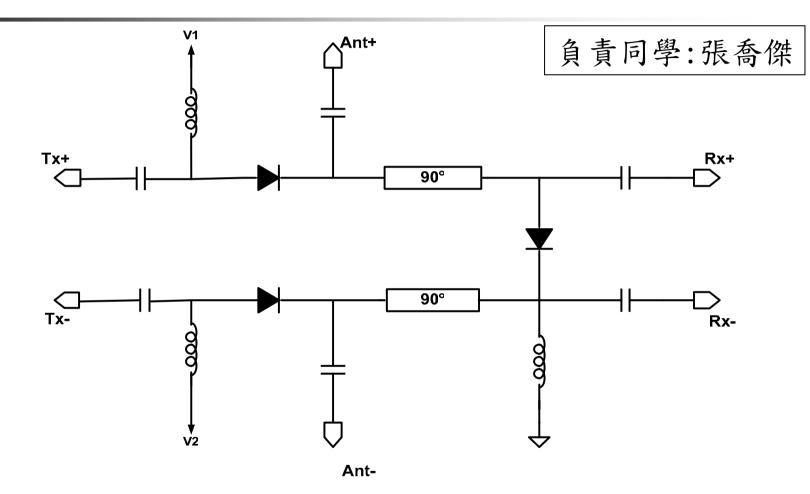

### 2. Differential T/R Switch

Three PIN DiodesNo DC Power consumption at Receiving Mode

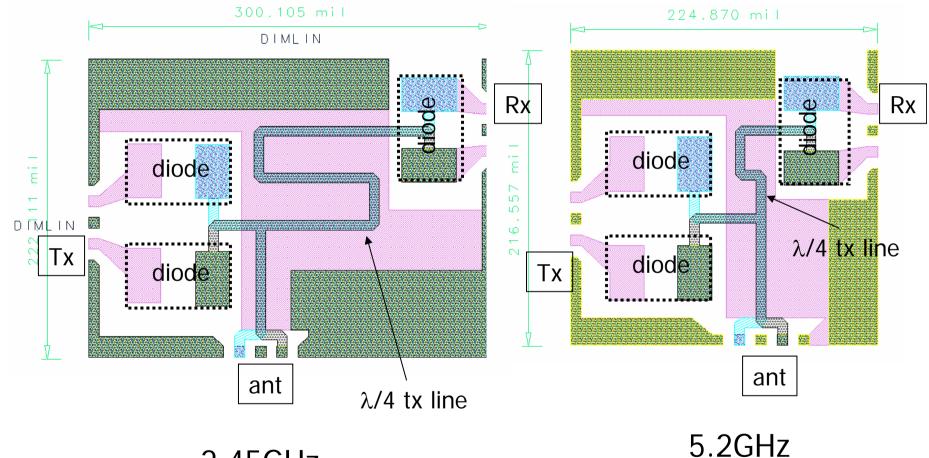

#### LTCC Layout @2.45GHz and 5.2GHz

2.45GHz

# 802.11 a/g Simulation Data

| 802.11g                | Mode          |         |  |

|------------------------|---------------|---------|--|

| Parameter              | <b>RX(0V)</b> | TX(3mA) |  |

| Insertion Loss@2.45GHz | 0.5dB         | 1.84dB  |  |

| Isolation TX/RX        | 45.9dB        | 45.9dB  |  |

| Isolation ANT/RX       |               | 30.16dB |  |

| Isolation TX/ANT       | 46.2dB-       |         |  |

| Power Handling         | 23dBm         | 23dBm   |  |

| 802.11a                | Mode          |         |  |

|------------------------|---------------|---------|--|

| Parameter              | <b>RX(0V)</b> | TX(3mA) |  |

| Insertion Loss@5.25GHz | 2.5dB         | 1.836dB |  |

| Isolation TX/RX        | 45dB          | 18.5dB  |  |

| Isolation ANT/RX       |               | 17.6dB  |  |

| Isolation TX/ANT       | 42dB          |         |  |

| Power Handling         | 23dBm         | 23dBm   |  |

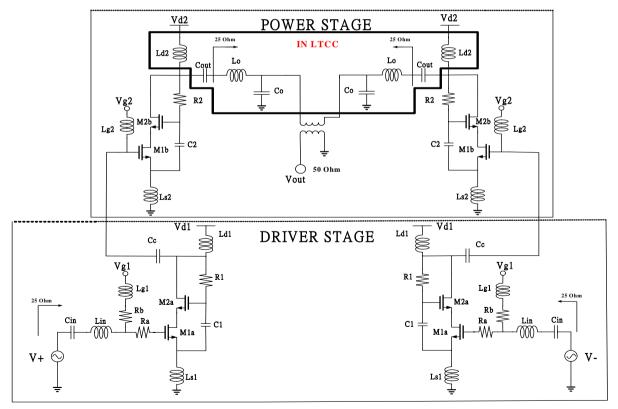

#### 3. Differential Self-biased PA for 802.11a

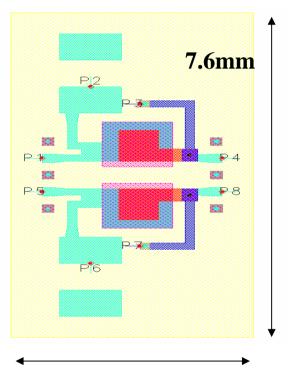

- Two stage differential PA, TSMC 0.18 CMOS 負責同學:黃奇順 process

- Output and input both match to  $50 \Omega$

- Driver stage is class A, power stage is class AB

#### Layout and simulation results

| Technology                                        | WLAN 802.11a 規格[1],<br>[6] | TSMC 0.18um<br>1P6M RF_CMOS |

|---------------------------------------------------|----------------------------|-----------------------------|

| Supply Voltage                                    | 1.8 V                      | 1.8 V                       |

| Center Frequency                                  | 5.25GHz                    | 5.25 GHz                    |

| Output Power (Psat)                               | >23 dBm                    | 23.2 dBm                    |

| Power Added Efficiency (PAE)<br>@ Pout = 23.2 dBm | >15 %                      | 38 %                        |

| Output P1dB                                       | >19 dBm                    | 19.497 dBm                  |

| Output IP3                                        | >26 dBm                    | 28.8734 dBm                 |

| Power Gain @ Pin = -12.5dBm                       | 20 dB                      | 19.5 <b>d</b> B             |

| DC current of driver stage                        |                            | 70.64mA                     |

| DC current of power stage                         |                            | 72.8mA                      |

**4 mm**