# Low-voltage CMOS four-quadrant multiplier based on square-difference identity

S.-I.Liu C.-C.Chang

Indexing terms: Four-quadrant analogue multiplier, VLSI circuits, Analogue signal processing

Abstract: A low-voltage CMOS four-quadrant multiplier based on the square-difference identity  $([a + b]^2 - a^2 - b^2)$  is presented. This circuit has been implemented in a 0.8µm single-poly double-metal *n*-well CMOS process. Experimental results show that for a power supply of ±1.5V, the linear input range of this multiplier is within ±0.5V with the linearity error less than 1%. The total harmonic distortion is less than 1% with input range up to ±0.5V. The -3dB bandwidth of this multiplier is measured to be about 1MHz. Moreover, it can operate satisfactorily regardless of the transistor body connection. This circuit is expected to be useful in low-voltage analogue signal-processing applications.

## 1 Introduction

The reduction of the minimum feature size of an MOS transistor for digital VLSI circuits has been ongoing for the past few decades. As the channel length is scaled down into deep-submicrometre dimensions, the lower power supply voltage is required to ensure the device reliability [1]. To be compatible with digital VLSI technologies, analogue integrated circuits, which can operate at low supply voltages, are also receiving significant attention. A four-quadrant analogue multiplier is a very useful building block in many circuits such as adaptive filters, frequency doublers and modulators. Recently, some four-quadrant multipliers suitable for low-voltage operation have been developed [2-5]. Several of these multipliers exploited MOS transistors in the triode region. Although triode-based multipliers have the better harmonic performance than saturationbased ones for operating in low supply voltages [2], the frequency response of the triode-based multipliers is limited and additional level-shift circuits for the input signals are required. In this paper a low-voltage CMOS four-quadrant multiplier using transistors operating in the saturation region is presented. This circuit has been implemented in a 0.8µm single-poly double-metal CMOS process. Experimental results demonstrate the feasibility of the proposed multiplier.

### © IEE, 1996

IEE Proceedings online no. 19960479

Paper first received 25th October 1995 and in revised form 11th March 1996

The authors are with the Department of Electrical Engineering, National Taiwan University, Taipei, Taiwan 10664, Republic of China

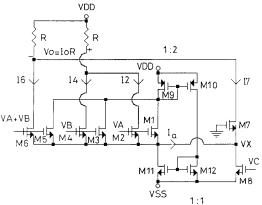

## 2 Circuit description

To realise the proposed multiplier the basic idea is based on the square-difference identity  $([a + b]^2 - a^2 - b^2 = 2ab)$  [6–9]. Moreover, low-voltage designs must avoid stacking two or more transistors in series and the output must be taken from the drains of transistors to create a full-swing output signal. The proposed CMOS multiplier is shown in Fig. 1. The drain current  $I_D$  of an NMOS device can be described by

$$I_D = K (V_{GS} - V_T)^2$$

(1)

where K is the transconductance parameter,  $V_{GS}$  is the gate-to-source voltage and  $V_T$  is the threshold voltage, respectively. Assume that the transistors,  $M_1$  to  $M_7$ , are perfectly matched with the identical parameters K and  $V_T$ . Assume that all the MOS devices in Fig. 1 were biased in saturation. Let the aspect ratio of  $M_{10}$  be twofold that of  $M_9$  and those of  $M_{11}$  and  $M_{12}$  be equal, too. The drain current of  $M_9$  is equal to a half sum of currents of  $M_1$  through  $M_6$ . Since the current of  $M_{11}$  $(M_{12})$  is equal to that of  $M_{10}$  (i.e. twice current of  $M_9$ ), so the current mirrors consisting of  $M_9$  through  $M_{12}$ will force the current  $I_a$  to zero. This positive feedback loop technique has been used to design operational transconductance amplifiers and active resistors [10, 11]. The working principle of the proposed multiplier is described as follows.

Fig.1 Proposed CMOS four-quadrant multiplier

The current  $I_7$  that flows through  $M_7$  can be expressed by

$$I_7 = K(-V_X - V_T)^2$$

(2)

The same current  $I_7$  that flows through  $M_8$  can be given as

$$I_7 = K_8 (V_C - V_{SS} - V_{T8})^2 \tag{3}$$

IEE Proc.-Circuits Devices Syst., Vol. 143, No. 3, June 1996

where  $K_8$  and  $V_{T8}$  is the transconductance parameter and threshold voltage of the device, M<sub>8</sub>.

According to eqns. 2 and 3, the following relation can be obtained:

$$V_X = \sqrt{\frac{K_8}{K}} (V_{SS} - V_C) - V_T + \sqrt{\frac{K_8}{K}} V_{T8}$$

(4)

Furthermore, the drain currents of the devices  $M_2$ ,  $M_4$ and  $M_6$  can be expressed as

$$I_2 = K(V_A - V_X - V_T)^2$$

(5)

$$I_4 = K(V_B - V_X - V_T)^2$$

(6)

$$I_6 = K(V_A + V_B - V_X - V_T)^2$$

(7)

Thus, the output current,  $I_o$ , of this multiplier can be defined and expressed as

$$I_{\rm o} = I_7 + I_6 - I_2 - I_4 = 2KV_A V_B \tag{8}$$

To guarantee linear operation for this circuit, the following constraints should be satisfied:

$$\min(V_A, V_B, V_A + V_B) > \sqrt{\frac{K_8}{K}}(V_{SS} - V_C) + \sqrt{\frac{K_8}{K}}V_{T8}$$

(9)

Because the devices  $M_1$  to  $M_7$ , are biased with equal source-to-substrate voltages, they need not be built in individual wells, which will result in a saving of chip area. Moreover, the simple structure of this multiplier will be suitable for low supply voltages.

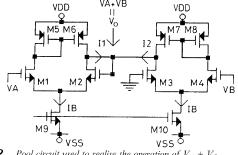

**Fig.2** Pool circuit used to realise the operation of  $V_A + V_B$

The operation of  $V_A + V_B$  can be realised using the circuit in Fig. 2. This circuit is called pool circuit [12-14]. Assume that the transistors in Fig. 2 are biased in the saturation region. The currents  $I_1$  and  $I_2$  in Fig. 2 can be expressed as

$$I_1 = K(V_A - v_o)\sqrt{\frac{2I_B}{K} - (V_A - v_o)^2}$$

(10)

$$I_2 = K V_B \sqrt{\frac{2I_B}{K} - V_B^2} \tag{11}$$

Therefore, at the equilibrium state,

$$_{\circ} = V_A + V_B \tag{12}$$

Using the circuit in Fig. 2 to realise the operation  $V_A$  +  $V_B$ , a four-quadrant multiplier can be achieved. The linear input range of this multiplier is limited once both the magnitudes of  $V_A$  and  $V_B$  are positive or negative. The magnitude of  $V_A + V_B$  approaching to the supply voltage will degrade the operation of the pool circuit and the proposed multiplier.

Table 1: Aspect ratios for all devices in Figs. 1 and 2

| Fig. 1 | Device  | M <sub>1</sub> M <sub>7</sub> | M <sub>8</sub> , M <sub>11</sub> , M <sub>12</sub> | M <sub>9</sub>                   | M <sub>10</sub> |

|--------|---------|-------------------------------|----------------------------------------------------|----------------------------------|-----------------|

|        | Wµm/Lµm | 5/20                          | 20/5                                               | 10/5                             | 20/5            |

| Fig. 2 | Device  | $M_1 - M_4$                   | $M_5-M_8$                                          | M <sub>9</sub> , M <sub>10</sub> |                 |

|        | Wµm/Lµm | 8/5                           | 5/5                                                | 20/5                             |                 |

IEE Proc.-Circuits Devices Syst., Vol. 143, No. 3, June 1996

#### **Experimental results** 3

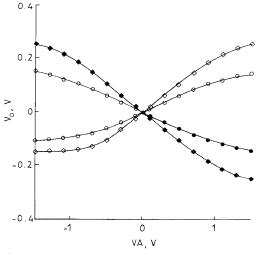

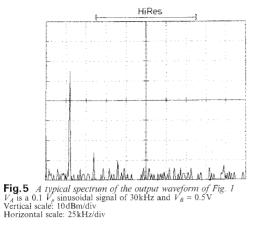

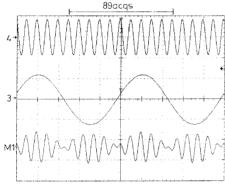

This circuit has been implemented in a 0.8µm singlepoly double-metal *n*-well CMOS process. The layout photograph for the multiplier in Fig. 1 is shown in Fig. 3. The aspect ratios for all devices in Figs. 1 and 2 are listed in Table 1. The power supply voltages are  $\pm 1.5$ V and  $V_C = -0.5$ V. The measured transfer curves of the multiplier are shown in Fig. 4. The circuit has a nonlinearity error less than 1% over ±0.5V input range. The total harmonic distortion was less than 1% for  $|V_A|$ < 0.5V and  $V_B = 0.5$ V. A typical spectrum of the output waveform of the multiplier is shown in Fig. 5 where  $V_A$  is a 0.1  $V_p$ , 30kHz sinusoidal signal and  $V_B =$ 0.5V. Fig. 6 shows the modulation application with  $V_B$ (the upper trace, 50 mV/div) is a 0.04  $V_p$  sinusoidal signal of 10kHz and  $V_A$  (the middle trace, 500mV/div) is a 0.6  $V_p$  sinusoidal signal of 1kHz. The -3dB bandwidth was measured to be about 1MHz.

Fig.3 Layout photograph for the multiplier in Fig. 1

Measured transfer curves of the proposed multiplier in Fig. 1 Fig.4 051 = -0.5 vis  $\pm 0.645 V$  and  $\pm 0.327 V$

| A changes nom     | 1.0 | ιo | 1.5 V |  |

|-------------------|-----|----|-------|--|

| $V_{R} = 0.645 V$ |     |    |       |  |

|                   |     |    |       |  |

| $V_B = 0.372 V$   |     |    |       |  |

|                   |     |    |       |  |

**g.6** Measured modulator application of the multiplier (the upper trace, 50mV/div) is a 0.04  $V_p$  sinusoidal signal of 10kHz (the middle trace, 500mV/div) is a 0.6  $V_p$  sinusoidal signal of 1kHz Fig.6 Modulated output (the lowest trace) is 50 mV/div Horizontal scale is 0.2 ms/div

#### 4 Conclusions

In this paper, a new low-voltage CMOS four-quadrant multiplier has been proposed. It has been fabricated in a 0.8µm single-poly double-metal n-well CMOS process. This multiplier is expected to be useful in low-voltage analogue-signal processing applications.

#### 5 Acknowledgment

The authors would like to thank the useful comments of the reviewers. The authors would like to thank the National Science Council for financial supporting and thank the Chip Implementation Center (CIC), National Science Council, Taiwan, for the fabrication of the test chip. This work was sponsored by NSC-85-2215-E-002-021.

#### References 6

- CHUNG, J.E., JENG, M.C., MOON, J.E., KO, P.K., and HU, C.: 'Performance and reliability design issue for deep-submi-crometer MOSFET's', *IEEE Trans. Electron Devices*, March 1991, **38**, pp. 545–554 1

- COBAN, A.L., and ALLEN, P.E.: 'Low-voltage four-quadrant analogue CMOS multiplier', *Electron. Lett.*, June 1994, **30**, pp. 1044–1045

- LIU, S.I.: 'Low voltage CMOS four-quadrant multiplier', *Electron. Lett.*, Dec. 1994, **30**, pp. 2125–2126 TSAY, J.H., LIU, S.I., and WU, Y.P.: 'CMOS four-quadrant 3

- Δ structure', *Electron. Lett.*, June, 1995, **31**, pp. 962–963

- KIMURA, K.: 'A dynamic bias current techniques for a bipolar exponential-law element and a square-law element usable with 5 HONG, Z., and MELCHIOR, H.: 'Analogue four-quadrant

- HONG, Z., and MELCHIOR, H.: 'Analogue four-quadrant CMOS multiplier with resistors', IEE Electron. Lett., 1985, 21, 6 pp. 531-532

- KIMURA, K., 'Four-quadrant analog multiplier circuit of float-ing input type'. US patent 5 187 682, 1993 KIMURA, K.: 'An CMOS four-quadrant analog multiplier based on the multitail technique using a quadritail cell as a multiplier core'. *IEEE Trans. Circuits Syst. I*, Aug. 1995, **42**, pp. 448–454 8

- 9 SAXENA, N., and CLARK, J.J.: 'A four-quadrant CMOS ana-

- by SAXERA, N., and CEARK, J.J.: A full-quadrant CMOS analog multiplier for analog neural networks', *IEEE J. Solid-State Circuits*, June 1994, **29**, pp. 746–749

10 NOCETI FIHO, S., and SCHNEIDER, M.C.: 'New CMOS OTA for fully integrated continuous-time circuit applications', *Electron. Lett.*, 1989, pp. 1674–1675

10 SAVENAL M., CMOS CONSTRUCTION (2017)

- Electron. Lett., 1999, pp. 107+1073

SAKURAI, S., and ISMAIL, M.: 'A CMOS square-law programmable floating resistor independent of the threshold voltage', *IEEE Trans. Circuits Syst. II*, Aug. 1992, **39**, pp. 565-574

TORRANCE, R.R., VISWANATHAN, T.R., and HAN-TORRANCE, R.R., VISWANATHAN, T.R., AND HAN-AND HAN-AND HAN-TORRANCE, R.R., VISWANATHAN, T.R., AND HAN-TORRANCE, R.R., VISWANATHAN, T.R., YISWANATHAN, T.R., YISWANATHAN, T.R., YISWANATHAN, T.R., YISWANATHA

- *TEEE Trans. Circuits Syst. 11*, Aug. 1992, **39**, pp. 565–574 TORRANCE, R.R., VISWANATHAN, T.R., and HAN-SON, J.V.: 'CMOS voltage to current transducers', *IEEE Trans. Circuits Syst.*, Nov. 1985, **32**, pp. 1097–1104 TSAY, S.W., and NEWCOMB, R.: 'A neuro-type pool arithme-tic unit'. Proceedings of the IEEE ISCAS'91, Singapore, 1991, pp. 2518–2521

- 13

- 14 LIU, S.I., and CHANG, C.C.: 'CMOS analog divider and four-quadrant multiplier using pool circuits', *IEEE J. Solid-State Cir-cuits*, Sept 1995, **30**, pp. 1025–1029