# A 10.8-mW Low-Noise Amplifier in 0.35-µm SiGe BiCMOS for UWB Wireless Receivers

Ming-Da Tsai, Chin-Shen Lin, Kun-You Lin, and Huei Wang

Department of Electrical Engineering and Graduate Institute of Communication Engineering, National Taiwan University, Taipei, Taiwan, R.O.C.

E-mail: hueiwang@ew.ee.ntu.edu.tw; Tel: +886-23635251-317; Fax: +886-2368-3824

Abstract — A UWB low-power and low-noise amplifier is proposed. The UWB LNA achieves better than 14.5-dB gain with 10.8-mW power consumption. The measured minimum noise figure is 3.1 dB and lower than 5.4 dB in the desired band. This MMIC is implemented in a commercial 0.35- $\mu$ m SiGe BiCMOS technology and occupies total chip size of only 0.74 mm² including all testing pads.

Index Terms — RFIC, low power, Silicon, SiGe BiCMOS, UWB, LNA.

### I. INTRODUCTION

UWB system is a new wireless technology capable of transmitting data over a wide spectrum of frequency bands with very low power and high data rates [1]-[3]. Although the UWB standard (IEEE 802.15.3a [2]) has not been completely defined, most of the proposed applications are allowed to transmit in a band between 3.1-10.6 GHz.

In recent years, narrow-band LNA designs have employed inductive source degeneration to achieve good input matching [4]-[7]. This technique also yields nearly optimal noise figure at the resonance frequency of the input network. Some low-noise amplifiers have been demonstrated for wideband applications [8]-[19]. A 30-mW high-gain LNA using LC-ladder matching network was proposed and implemented in 0.18-µm SiGe HBT technology [8]. A 3.4-6.9-GHz LNA with inductive source degeneration consumes 3.5 mW for applications of low-end UWB radio spectrum [9]. A DC-7.8 GHz LNA using 0.25-µm SiGe BiCMOS process was demonstrated for UWB and optical communication [10]. A Chebyshev matching CMOS LNA provides good input return loss with the noise figure from 4 to 9 dB in the desired band [12]. A conventional CMOS distributed amplifier (DA) can cover full-band UWB with low NF, but consumes high dc power [11]. A modified low-power distributed amplifier was proposed and demonstrated in [13]. Recently, two UWB LNA with resistive feedback technique were also demonstrated [14]-[15]. An LNA in 180-GHz SOI SiGe technology can operate at 14.5 mW

and only 2.7-3.9-dB NF, but the input return loss is only better than 2 dB [14]. The other demonstrates high gain and good NF performance in 150-GHz SiGe HBT process, but the dc power consumption is about 42.5 mW [15].

In this paper, a wideband low-noise amplifier in a low-cost process is demonstrated. The input impedance matching is achieved by multi-section structure in conjunction with cascode cell, which is terminated by inductive peaking and Darlington cascode configuration. The supply voltage is 1.8 V and consumes 6 mA. This MMIC can achieve a high gain and low noise figure performance with low power consumption even it is implemented in a 0.35-µm SiGe BiCMOS technology.

## II. CIRCUIT DESIGN AND IMPLEMENTATION

The UWB LNA was implemented using TSMC commercial 0.35- $\mu$ m 3P3M SiGe BiCMOS technology, which provides three poly layers for the emitters and bases of the SiGe HBT and the gates of the CMOS transistors; three metal layers for interconnection. The HBT can offer  $f_{\text{max}}$  of 57 GHz. This process with low-resistivity substrate (~ 10 S/m) provides monolithic inductors with quality factor below 10.

One popular way to achieve a 50 ohm input resistance of an LNA is by inductive emitter degeneration as shown in the schematic diagram of Fig. 1. The use of the emitter degenration can enhance the linearity and provide the input resistance, which is necessary for input matching. The implementation of the matching network can be easily derived as:

$$Z_{in}(s) = \frac{1}{sC_{be}} + s(L_b + L_e) + \frac{g_m L_e}{C_{be}}$$

$$= \frac{s^2 C_{be}(L_b + L_e) + sg_m L_e + 1}{sC_{be}}$$

The emitter degeneration inductance  $L_{\rm e}$  can transform the input impedance to a real part, generally designed to 50 ohm. The imaginary part of the input impedance can

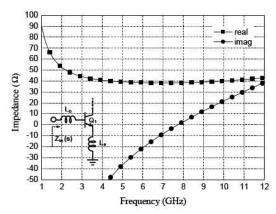

be resonated with base and emitter inductance ( $L_b$  and  $L_e$ ). However, this impedance matching scheme is only suitable for narrow band application. Fig. 1 shows the simulated input impedance of the HBT transistor  $(0.3\times20.3 \ \mu\text{m}^2)$  with emitter inductive degeneration  $(L_s)$ and series based inductance (Lb). According to the first order equation for input matching, the emitter degeneration can be determined by the transistor's transconductance (g<sub>m</sub>) and intrinsic base-emitter capacitance  $(C_{be})$ . The selected  $L_{e}$  is about 0.2 nH for increasing the input resistance to match system impedance. Since our design goal is to achieve low input return loss, the input matching resistance of 40  $\Omega$  is selected to achieve better than 10-dB input return loss, which is determined by the value of L, and trade off with small-signal gain. The series base inductance  $(L_b)$  can be used to compensate the intrinsic base-emitter capacitance (C<sub>k</sub>). The zero crossing point of imagine part at 8 GHz can also be observed in Fig. 1, which means input impedance matching is only achieved around 8 GHz. For UWB band (3.1-10.6 GHz) application, the conventional impedance matching is difficult to meet the specification.

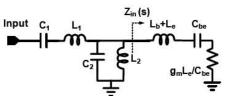

According to the above-mentioned analysis, more complex matching network is required to fulfill the UWB specifications. Another matching solution, shown in Fig. 2, expands the use of an inductively degenerated common-emitter amplifier by embedding the input network of the amplifying device in a multi-section reactive network so that the overall input reactance is resonated out over a wider bandwidth, which was first implemented in CMOS technology [12].

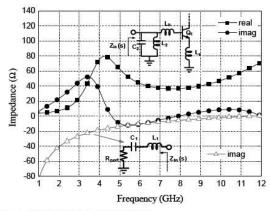

Since the input reactance of the conventional matching network shown in Fig. 1 is capacitive at lower frequency and inductive at higher frequency, the additional elements should compensate the reactance and maintain the resistance over the wide frequency band. Since the original matching is set at about 8 GHz, a shunt LC element is also set to be resonance at 8 GHz and provides inductive/capacitance at low/high frequency. This can potentially cancel the reactance of frequency response in Fig. 1. Fig. 3 illustrates the resistance and reactance of the compensated response. The reactance at 3-4 GHz is still difficult to be canceled. The series LC provides low-frequency capacitance to cancel out the reactance over 3-4 GHz, as shown in Fig. 3. The overall simulated input return losses from 3.1-10.6 GHz are all better than 10 dB.

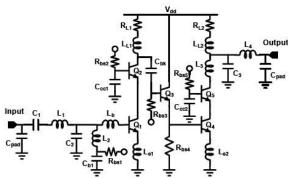

The overall circuit schematic is shown in Fig. 4. The input active gain cell ( $Q_1$  and  $Q_2$ ) is cascode configuration. The load of the cascode cell ( $R_{\rm L1}$  and  $L_{\rm L1}$ ) is inductive peaking to extend operation bandwidth. The following stage is Darlington cascode configuration ( $Q_3$ ,  $Q_4$ , and  $Q_5$ )

to achieve higher gain performance and directly coupled to the first stage to reduce circuit complexity and chip size. However, the stability of the Darlington cascode configuration is also an important issue. The emitter inductive degeneration ( $L_{\rm e2}$ ) can improve the stability. The output load is also inductive peaking ( $R_{\rm L2}$  and  $L_{\rm L2}$ ) for bandwidth extension and output matching, which is associated with  $L_{\rm 3}$ ,  $L_{\rm 4}$  and  $C_{\rm 3}$ . The supply voltage is 1.8 V and consumes total current of 6 mA.

Fig. 1. Real and imaginary parts of input impedance of the HBT transistor with emitter inductive degeneration and series base inductance  $(L_h)$ .

Fig. 2. Schematic of the LNA input network.

Fig. 3. Simulated input impedance.

Fig. 4. Schematic of the wideband LNA

## III. MEASUREMENT RESULTS

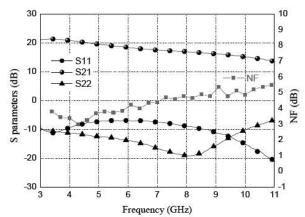

Fig. 5 shows chip photograph of the UWB LNA with chip size of only 0.93 mm × 0.76 mm. The UWB LNA was measured using on-wafer probing with GGB ground-signal-ground (GSG) probes. Fig. 6 shows the measured power gain and input/output return losses at 1.8-V supply and 6 mA. The power gain is better than 14.5 dB from 3 to 10.6 GHz while consuming 10.8 mW dc power. The input return loss is better than 7 dB and the output return loss is better than 10 dB in the entire desired band. The measured noise figure (NF) is also shown in Fig. 6. The noise figure is lower than 5.4 dB from 3.1 to 10.6 GHz. The lowest NF is 3.1 dB at 4.3 GHz.

The measured output  $P_{IdB}$  are between -14 ~ -12 dBm from 3.1-10.6 GHz. The measured input third-order intercept points (IIP3) is about -19 dBm from 3.1-10.6 GHz.

Fig. 5. Chip photograph of the multi-section UWB LNA (size:  $0.93 \text{ mm} \times 0.79 \text{ mm}$ ).

Fig. 6. Measured S parameters and noise figure.

### IV. CONCLUSION

low-power and low-noise amplifier 3.1-10.6-GHz ultra-wideband radio systems demonstrated in this paper. The broadband amplifier is based on multi-section input impedance matching and Darlington cascode configuration. The inductive peaking is also used to improved bandwidth performance. The MMIC achieves better than 14.5-dB gain with 10.8-mW power consumption. The I/O return losses are better than 7 and 10 dB, respectively. The measured noise figures are 3.1 to 5.4 dB from 3.1 to 10.6 GHz. The chip size is only 0.74 mm<sup>2</sup> including all testing pads. Table I summaries the recently reported LNAs for UWB applications. This MMIC can achieve a high gain and low noise figure performance with low power consumption even it is implemented in low-cost 0.35-um SiGe BiCMOS technology.

## ACKNOWLEDGEMENT

This work is supported in part by the MediaTek Fellowship and National Science Council of Taiwan, R.O.C. (NSC 93-2219-E-002-016, NSC 93-2219-E-002-024, NSC 93-2213-E-002-033, and NSC 93-2752-E-002-002-PAE). The chip is fabricated by Taiwan Semiconductor Manufacturing Company (TSMC) through National Chip Implementation Center (CIC) of Taiwan, R.O.C.

## REFERENCES

D. Porcino and W. Hirt, "Ultra-wideband radio technology: Potential and challenges ahead," *IEEE Commun. Mag.*, vol. 4, pp. 66–74, July 2003.

- [2] FCC, "Final Rule of the Federal Communications Commission, 47 CFR Part 15, Sec. 503," Federal Register, vol. 67, no. 95, May 2002.

- [3] http://www.ieee802.org/15/pub/TG3a.html.

- [4] D. K. Shaffer, and T. Lee, "A 1.5-V, 1.5-GHz CMOS low noise amplifier," *IEEE J. Solid-State Circuits*, vol. 32, pp. 745-759, Jun 1997

- [5] M. D. Tsai, H. Wang, J. F. Kuan, and C. P. Chao, "A miniature 4.3-7-GHz, 1-V CMOS LNA with helical inductors," in *IEEE European Microwave Conference*, Amsterdam, Oct. 2004.

- [6] T. K. K. Tsang and M. N. El-Gamal, "A fully integrated 1 V 5.8 GHz bipolar LNA," in *Proc. IEEE Int. Symp. Circuits and Systems (ISCAS'01)*, vol. 4, pp. 842–845, May 2001.

- [7] E. Imbs, I. Telliez, S. Detout, and Y. Imbs, "A low-cost-packaged 4.9-6 GHz LNA for WLAN application," in *IEEE MTT-S Dig.*, vol. 3, pp. 1569–1572, June 2003.

- [8] A. Ismail and A. Abidi, "A 3 to 10GHz LNA using a wideband LC-ladder matching network," *International* Solid-State Circuit Conf. Dig. Tech. Papers, pp. 384-385, Feb. 2004.

- [9] D. Barras, F. Ellinger, H. Jackel, and W. Hirt, "A low supply voltage SiGe LNA for ultra-wideband frontends," *IEEE Microwave and Wireless Component Letters*, vol. 14, no. 10, Oct. 2004

- [10] F. Ellinger, D. Barras, M. Schmatz, and H. Jackel, "A low-power DC-7.8 GHz BiCMOS LNA for UWB and optical communication," in *IEEE MTT-S Dig.*, pp. 13-16, June 2004.

- [11] R. C. Liu, C. S. Lin, K. L. Deng, and H. Wang, "A 0.5-14-GHz 10.6-dB CMOS cascode distributed amplifier," *IEEE VLSI Circuit Symp.*, pp.139-140, 2003.

- [12] A. Bevilacqua and Ali M Niknejad, "An ultra-wideband CMOS LNA for 3.1 to 10.6GHz wireless receivers," *International Solid-State Circuit Conf. Dig. Tech. Papers*, pp. 382-383, Feb. 2004.

- [13] M. D. Tsai, K. Y. Lin and H. Wang, "A 5.4-mW LNA using 0.35-μm SiGe BiCMOS technology for 3.1-10.6-GHz UWB wireless receivers," in *IEEE RFIC* Symp., pp. 335-338, Long Beach, June 2005.

- [14] N. Shiramizu, T. Masuda, M. Tanabe, and K. Washio, "A 3-10 GHz bandwidth low-noise and low-power amplifier for full-band UWB communications in 0.25-µm SiGe BiCMOS technology," in *IEEE RFIC Symp.*, pp. 39-42, Long Beach, June 2005

- [15] J. Lee and J. D. Cressler, "A 3-10 GHz SiGe resistive feedback low noise amplifier for UWB applications," in *IEEE RFIC Symp.*, pp. 545-548, Long Beach, June 2005

- [16] W. Lee and I. W. Filanovsky, "2 V 3 GHz low-noise bipolar wideband amplifier," in *Proc. Canadian Conf. Electrical Computer Engineering*, pp. 627–632, May 1999.

- [17] J. Sadowy et al., "Low noise, high linearity, wide bandwidth amplifier using a 0.35μm SiGe BiCMOS for WLAN applications," in *IEEE Radio Frequency Integrated* Circuits (RFIC) Symp., pp. 217–220, June 2002.

- [18] H. Ainspan, M. Soyuer, J.-O. Plouchart, and J. Burghartz, "A 6.25-GHz low DC power low-noise amplifier in SiGe," in *IEEE Custom Integrated Circuits Conf.*, pp. 177–180, May 1997

- [19] F. Bruccoleri et al., "Noise canceling in wideband CMOS LNAs," *International Solid-State Circuit Conf. Dig. Tech.* Papers, pp. 406-407, Feb. 2002.

Table I

RECENTLY REPORTED PERFORMANCES OF UWB LOW NOISE AMPLIFIERS.

| Process                 | Freq.<br>(GHz) | Gain<br>(dB) | NF<br>(dB) | I/O RL<br>(dB) | Chip Size<br>(mm²) | Total P <sub>dd</sub><br>(mW) | Topology                                      | Ref.            |

|-------------------------|----------------|--------------|------------|----------------|--------------------|-------------------------------|-----------------------------------------------|-----------------|

| 0.18µm SiGe<br>HBT      | 3~10           | 21           | < 4.2      | < -9           | 1.8                | 30*                           | LC-ladder match                               | ISSCC04<br>[8]  |

| 0.25μm SiGe<br>HBT      | 3.4 ~ 6.9      | 10           | < 5        | < -6           | 1.39               | 3.5                           | Narrow-band L<br>degeneration                 | MWCL04<br>[9]   |

| 0.25µm SiGe<br>BiCMOS   | DC ~ 7.8       | 10.6         | < 4.4      | <-7.8          | 0.45               | 6.5                           | Input active match                            | IMS04<br>[10]   |

| 0.18µm<br>CMOS          | 0.5 ~ 14       | 10.6         | < 5.4      | < -11          | 1.6                | 54 <sup>+</sup>               | Conventional DA                               | VLSI03<br>[11]  |

| 0.18µm<br>CMOS          | 2.3 ~ 9.2      | 9.3          | < 9.5      | < -10          | 1.1                | 9*                            | Band-pass<br>Chebychev match                  | ISSCC04<br>[12] |

| 0.35µm SiGe<br>BiCMOS   | 3.1 ~ 10.6     | 10           | < 6.4      | < -7           | 0.47               | 5.4                           | Modified<br>low-power DA                      | RFIC05<br>[13]  |

| 0.25-μm SOI<br>SiGe HBT | 3 ~ 10         | 22           | < 3.9      | < -2 / <-10    | 0.49               | 13.2                          | Resistive FB and CB                           | RFIC05<br>[14]  |

| Advanced<br>SiGe HBT    | 3 ~ 10         | 20           | < 4.5      | < -10 / < -8   | 0.52               | 42.5                          | Resistive FB                                  | RFIC05<br>[15]  |

| 0.35μm SiGe<br>BiCMOS   | 3.1 ~ 10.6#    | > 14.5       | 3.1 - 5.4  | < -7 / < -10   | 0.74               | 10.8                          | Multi-section<br>match, Darlington<br>Cascode | This Work       |

<sup>+:</sup> Bias by off-chip Bias-T. \*: excluding power consumption of output stage for output matching.

#: defined by gain of better than 14.5 dB