# A Locally Matching Technique for Broadband Flip-chip Transition Design \*

# Chun-Long Wang and Ruey-Beei Wu

Department of Electrical Engineering and Graduate Institute of Communication Engineering, National Taiwan University, Taipei, Taiwan, 10617, ROC

Abstract — A locally matching technique is proposed in this paper to improve the wideband performance of flip-chip transition. The gap width of the CPW line in the flip-chip bump pad region is enlarged for achieving larger inductance to compensate the capacitance at the transition, making the approximate impedance close to 50 \( \Omega\$. An equivalent circuit is derived from the frequency response of the transition simulated by Sonnet and is used to control the resonance frequency of the structure. With properly chosen value of the enlarged width, the resonant dip can be controlled to improve return loss over a band from DC to 60GHz. Measurement data of the scaled structure is in good agreement with the simulation results, which validates the proposed design idea.

#### I. INTRODUCTION

Flip-chip transition has become a promising technique over bond-wire in the microwave and millimeter wave frequency, due to its features of short and stable electrical interconnection, low cost, and high reliability. As frequency goes higher, the parasitic effects of the flip-chip transition may result in performance degradation. They should be considered carefully in order to achieve good transition from DC up to millimeter wave spectrum.

For flip-chips of typical dimensions, the frequency response has been examined to yield an accurate equivalent circuit model which shows overall capacitive property [1]. It was thus suggested that the bump pad be kept as short as possible to lessen the capacitance at initial design [2]. This usually causes great concern in fabrication. Another approach was a staggered design in the central line of CPW [3]. The return loss was improved, but with the increase in the chip areas as trade off.

Recently, some investigators suggested to use a high impedance line or matching circuits on the motherboard to compensate the excessive capacitance of the transition [4]-[6]. These techniques are satisfactory to optimize the transition over certain frequency band, but difficult to cover a wide band from DC up to millimeter wave spectrum. One way to enhance the transition bandwidth is to reduce the longitudinal dimension of the high impedance line or the matching circuits. Based on this concept, a locally matching technique is proposed in this paper by designing the transition transversely rather than

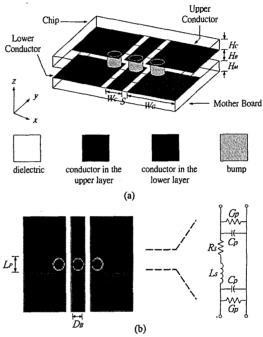

Fig. 1. The structure of the traditional flip-chip transition (a) 3-D view (b) upper view and its equivalent circuit.  $W_C$ =200 $\mu$ m, S=70 $\mu$ m,  $W_G$ =600 $\mu$ m,  $H_C$ = $H_B$ = $H_M$ =127 $\mu$ m,  $D_B$ =160 $\mu$ m,  $L_P$ =200 $\mu$ m,  $\varepsilon_I$ =10.2.

longitudinally. Both the simulation and measurement are performed and compared to validate the design concept.

#### II. COMPENSATION ON ONE SIDE

# A. Hi-impedance compensation

Consider the structure of a traditional flip-chip transition snown in Fig. 1(a). Fig. 1(b) shows its top view together with the equivalent circuit which resembles a low pass filter of order N=3. The element values can be determined

<sup>\*</sup> This work was supported in part under the Grant 89-E-FA06-2 by Ministry of Education and NSC 90-2219-E002-005 by National Science Council. Republic of China.

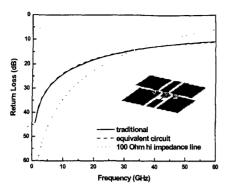

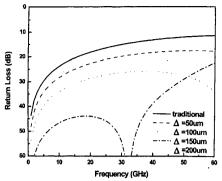

Fig. 2. The return loss versus frequency of the traditional flip-chip transition and hi-impedance compensation structures.

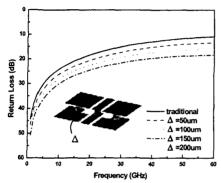

Fig. 3. The return loss versus frequency for the structure with the ground retreat  $\Delta$  on the motherboard as a parameter.

from the comparison with the frequency response of the transition simulated by Sonnet. It is found that the series resistance  $R_S$  and shunt conductance  $G_P$  are small and can be neglected. With the geometric dimensions given in Fig. 1, the series inductance  $L_S$  is found to be 69.95pH and the shunt capacitance  $C_P$  is 34.81fF. Since  $Z_D = \sqrt{L_S/2C_P} \equiv 32\Omega$  is much smaller than the system of characteristic impedance  $Z_O$ =50  $\Omega$ , the transition shows overall capacitive property.

Fig. 2 compares the simulation results of return loss (RL) for the traditional flip-chip transition and those by the equivalent circuit in Fig. 1(b). The agreement verifies the correctness of such an equivalent circuit. The results by adopting the hi-impedance compensation technique [5]-[6] is also shown on this figure. It is clear that the return loss is improved at low frequency band only. From an equivalent circuit point of view, the addition of hi-impedance line which contributes a large series inductance to form a low pass filter with order N=4 will degrade its high frequency performance. In addition, the overall effect

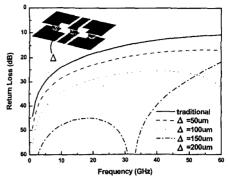

Fig. 4. The return loss versus frequency for the structure of the locally matching structure.

of the hi-impedance line is no more a lumped inductance when its length reaches one-tenth of a guided wavelength at high frequencies.

## B. Increasing the gap width on motherboard

To improve the high frequency performance of the flipchip, the values of the series inductance  $L_S$  and the shunt capacitance  $C_P$  should be carefully controlled. Intuitively, a good transition can be achieved if both the values of the series inductance or shunt capacitance are reduced to make the associated impedance  $Z_p = \sqrt{L_S/2C_P}$  matched to 50  $\Omega$ .

Subject to the constrain by the wiring rule in the fabrication process that the length and aspect ratio of bump is maintained, the value of the inductance could not be reduced by this way. The remaining way is to reduce the value of the shunt capacitance in the discontinuity. Fig. 3 shows the simulation results of return loss in which the gap width on the motherboard is enlarged to reduce the shunt capacitance. It can be seen that the return loss is improved with a suitable gap width, as evident from the equivalent circuit in Fig. 1(b). It deserves mentioning that the improvement covers a large bandwidth since the matching structure occupied a very small area.

However, the overall capacitance of the discontinuity is contributed by the shunt capacitance  $C_P$  on both the motherboard and the chip sides. Reducing the capacitance on one side only will restrict the effectiveness of this design. Thus, it would be better to employ the idea of locally matching to reduce the values of the capacitance on both sides more efficiently.

# III. COMPENSATION ON BOTH SIDES

The locally matching structure is shown in the inset of Fig. 4. It is seen that both the ground conductor on the motherboard and chip are retreated by a distance  $\Delta$ . Fig. 4 also shows the frequency response of return loss with

Fig. 5. The return loss versus frequency for the equivalent circuit of the locally matching structure.

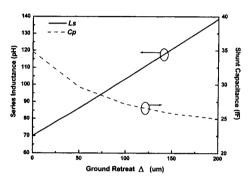

Fig. 6. The series inductance  $L_S$  and shunt capacitance  $C_P$  versus the ground retreat  $\Delta$ .

ground retreat  $\Delta$  as a parameter. By properly choosing the parameter, say  $\Delta$ =100  $\mu$ m, the return loss can be greatly improved over a wide band covering DC up to 60 GHz or more. The design is satisfactory and simple, but with some areas occupied in the transverse direction of the chip as trade off.

The equivalent circuit of the locally matching structure can be well represented as Fig. 1(b) including the effect of the step discontinuity since the size of the discontinuity is small as compared to one-tenth of the guided wavelength. The return loss of the equivalent circuit versus frequency is shown in Fig. 5. The excellent agreement with those in Fig. 4 verifies the correctness of this equivalent circuit. Fig. 6 shows the result of the series inductance  $L_S$  and shunt capacitance  $C_P$  versus the ground retreat  $\Delta$ . As  $\Delta$  increases, the capacitance decreases as expected while the inductance increases. Actually,  $\Delta$  has a more significant influence on the series inductance than on the shunt capacitance.

It is interesting to note the occurrence of the dip in the return loss versus the frequency for  $\Delta$ =150 $\mu$ m in Fig. 5. The resonant frequency, which corresponds to the dip of

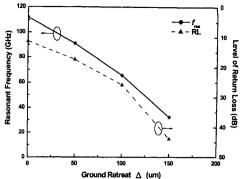

Fig. 7. The resonant frequency versus the reduced width  $\Lambda$

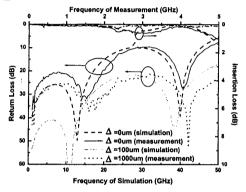

Fig. 8. Frequency response of the back-to-back transition structure for the comparison between simulation results and measurement data of ten times scaled model.

return loss can be derived from the equivalent circuit of Fig. 1(b). There are two solutions, one is f=0GHz and the other is:

$$f_{res} = \frac{1}{2\pi} \sqrt{\frac{1}{L_s C_p^2} (2C_p - \frac{L_s}{Z_o^2})}$$

(1)

At the open circuit limit that  $Z_O$  tends to  $\infty$ , the resonant frequency becomes  $f_{ret} = \sqrt{2/L_sC_P}/2\pi$  which corresponds to the resonance in the transverse direction of the flip-chip transition. Fig. 7 shows the value of resonant frequency versus the ground retreat  $\Delta$ . It can be seen that the value of the resonant frequency corresponding to  $\Delta$ =200 $\mu$ m does not exist because the value of  $Z_D$  is large than 50 $\Omega$ . Also shown in this figure is the level of return loss, which is defined as the local minimum of return loss before the resonant frequency  $f_{ret}$  for a given value of  $\Delta$  in Fig. 5. Based on this figure, the ground retreat  $\Delta$  can be chosen properly to determine the resonant frequency  $f_{ret}$  for the best transition performance over the desired bandwidth.

For experimental verification, two single locally matching structures are fabricated and connected back to back for measurement with ten times scaled up in all the geometric dimensions. The separation between the two single transitions is 22mm, which results in a multiple resonance frequency of 3.16GHz. The circuit is fabricated on the board of RT/Duroid 6010 and bump is formed with copper. The measurements are done on the Vector Network Analyzer HP8510C with the TRL calibration.

Fig. 8 shows the frequency response of the back-to-back transitions obtained by the simulation and measurement under ten times model. Good agreement between simulation and measurement can be seen from the figure except for a small shift in the resonance frequency. This may be contributed to the abrupt cut of the dielectric of the chip near the discontinuity or the misalignment of solder bumps in fabrication. For the insertion loss, the measurement shows the same tendency as the simulation results if the conductor and dielectric loss are not concerned

## IV. CONCLUSIONS

The hi-compensation structure can improve the performance of the flip-chip transition only in a limited frequency range due to its comparatively large size in longitudinal direction. The locally matching technique with ground retreat  $\Delta$  on the motherboard only can improve the return loss of the flip-chip, but the effectiveness is restricted by the capacitance of the discontinuity on the chip side. The idea of locally matching is also extended to both the motherboard and the chip sides in this paper. By properly choosing a suitable ground retreat  $\Delta$  to control the resonant frequency, the return loss of the flip-chip transition can be greatly improved over a wide frequency band with some occupied area on the transverse direction of chip as trade off.

### ACKNOWLEDGEMENT

The authors would like to thank Mr. Shih-Chieh Yen and Shih-Je Yang for helps on the circuit board fabrication and Mr. Wen-Hua Tu for the suggestions in measurement.

#### REFERENCES

[1] H. H. M. Ghouz and E. El-Aharawy, "An accurate equivalent circuit model of flip chip and via interconnects," *IEEE Trans. Microwave Theory Tech.*, vol. 44, no. 12, pp. 2543-2554, Dec. 1996.

- [2] M. Szymanowski and S. Safavi-Naeini, "Characterization of a flip-chip interconnect at frequencies up to 30 GHz," 2000 Canadian Conference on Electrical and Computer Engineering, vol. 2, pp. 784-787, 2000.

- [3] H. H. M. Ghouz and E. El-Aharawy, "Finite-difference time-domain analysis of flip-chip interconnects with staggered bumps," *IEEE Trans. Microwave Theory Tech.*, vol. 44, pp. 960-963, June 1996.

- [4] N. Iwasaki, F. Ishitsuka, and K. Kato, "High performance flip-chip technique for wide-band modeles," 1996 IEEE 5th Topical Meeting on Electrical Performance of Electronic Packaging, pp. 207-209, 1996.

- [5] W. Heinrich, A. Jentzsch, and G. Baumann, "Millimeterwave characteristics of flip-chip interconnects for multi-chip modules," *IEEE Trans. Microwave Theory Tech.*, vol. 46, pp. 2264-2268, Dec. 1998.

- [6] A. Jentzsch and W. Heinrich, "Theory and measurement of flip-chip interconnects for frequencies up to 100GHz," *IEEE Trans. Microwave Theory Tech.*, vol. 49, pp. 871-877, May, 2001.