## 行政院國家科學委員會專題研究計畫 期中進度報告

# 先進 CMOS 元件及製程研究--子計畫一: 適用於低溫基板製程之高品質絕緣膜形成技術(2/3)

期中進度報告(精簡版)

計畫類別:整合型

計畫編號: NSC 95-2221-E-002-358-

執 行 期 間 : 95 年 08 月 01 日至 96 年 07 月 31 日 執 行 單 位 : 國立臺灣大學電子工程學研究所

計畫主持人: 胡振國

處 理 方 式 : 期中報告不提供公開查詢

中 華 民 國 96年05月30日

# 行政院國家科學委員會補助專題研究計畫成果報告

先進 CMOS 元件及製程研究 — 子計畫一 : 適用於低溫基板製程之高品質絕緣膜形成技術(2/3)

計畫類別: 個別型計畫 整合型計畫

計畫編號:NSC95-2221-E-002-358

執行期間: 95年8月1日至96年7月31日

計畫主持人 : 胡振國 台大電子工程學研究所教授

計畫參與人員:張嘉華、陳志豪、王志慶、江榮進

成果報告類型(依經費核定清單規定繳交): 精簡報告 完整報告 本成果報告包括以下應繳交之附件:

赴國外出差或研習心得報告一份

赴大陸地區出差或研習心得報告一份

出席國際學術會議心得報告及發表之論文各一份

國際合作研究計畫國外研究報告書一份

處理方式:除產學合作研究計畫、提升產業技術及人才培育研究計畫、列管計

畫及下列情形者外 , 得立即公開查詢

涉及專利或其他智慧財產權, 一年 二年後可公開查詢

執行單位:台大電子工程學研究所

中 華 民 國 96 年 5月 25日

## 行政院國家科學委員會補助專題研究計畫期中成果報告

### 先進 CMOS 元件及製程研究

子計畫一:適用於低溫基板製程之高品質絕緣膜形成技術(2/3)

第二年(95/8~96/7)期中進度報告

計畫編號:NSC95-2221-E-002-358

主 持 人: 胡 振 國 台大電機工程學系/電子工程學研究所教授 共同參與研究生: 張嘉華、陳志豪、王志慶、江榮進

#### 一、 摘要:

本計畫在第二年度之主要研究成果可分為以傾斜晶圓濺鍍Hf金屬並以硝酸氧化再純水補償備製低溫HfO2高介電常數絕緣層技術、以純水應力陽極氧化生長法備製高品質超薄閘極氧化層技術、及以傾斜遮罩蒸鍍Al金屬並以硝酸氧化備製低溫Al<sub>2</sub>O<sub>3</sub>高介電常數絕緣層技術三大部份。三部份之執行均以低溫備製完成,適合低溫基板應用。

在以傾斜晶圓濺鍍Hf 金屬並以硝酸氧化再純水補償備製低溫 HfO<sub>2</sub> 高介電常數絕緣層技術部份,提出新穎特殊之傾斜晶圓來得到不同厚度 Hf 金屬,經過室溫硝酸氧化為 HfO<sub>2</sub> 再以純水陽極氧化補償漏電路徑,得到等效厚度可達 19 nm,崩潰電場可達 12 MV/cm,漏電流低且可靠性佳之低溫高介電常數絕緣層。

在以純水應力陽極氧化生長法備製高品質超薄閘極氧化層技術部份,延續第一年的研究成果,對p及n型基板之晶圓均進行研究比較,發現 MOS(p)與 MOS(n)元件氧化層之漏電流明顯較對照組減少,特性獲改善。

在以傾斜遮罩蒸鍍 AI 金屬並以硝酸氧化備製低溫 AI<sub>2</sub>O<sub>3</sub> 高介電常數絕緣層技術部份,將晶圓前方放置一遮罩,利用傾斜角度調整得到同一晶圓上有不同之鋁厚度,經由本單位提出之硝酸氧化法可得不同連續厚度變化之低溫 AI<sub>2</sub>O<sub>3</sub> 高介電常數絕緣層,特性穩定。

關鍵詞:高介電常數絕緣層、HfO<sub>2</sub>、Al<sub>2</sub>O<sub>3</sub>、應力陽極氧化

#### **Abstract:**

In the second year of this project, there are three main subjects studied. The first is the low temperature HfO<sub>2</sub> prepared by tilted sputtering of Hf metal and then followed by nitric acid oxidation compensated with anodization in D.I. water. The second is the preparation of high quality ultra-thin gate oxides by strain-oxidation technique carried out in D.I. water with bent wafer. The third is the preparation of Al<sub>2</sub>O<sub>3</sub> high-k dielectrics by shadow evaporation of Al film on a wafer and then oxidized by nitric acid. The above three works are related to low temperature which are suitable for low temperature substrate applications.

In the first subject of the low temperature HfO<sub>2</sub> prepared by tilted sputtering of Hf metal and then followed nitric by acid oxidation compensated with anodization in D.I. water, the wafer is tilted during sputtering to obtain continuously distributed thickness in one single substrate. The oxidized HfO2 was compensated by anodization in D.I. water to repair the leaky path in existing oxides. The smallest equivalent oxide thickness is 19 nm, the effective breakdown field is higher than 12 MV/cm, the leakage current is low and the reliability is satisfactory for the prepared low temperature high-k dielectrics.

In the second subject of the preparation of high quality ultra-thin gate oxides, the method as proposed in the first year was continuously studied. Both of p and n type wafers are used for comparison. The leakage currents for MOS(p) and MOS(n) structures with oxides prepared by strain-oxidation methods are obviously lower than those control samples under the same oxide thickness. The reliability for the former ones are also superior to the latter ones.

In the third subject of the preparing high-*k* Al<sub>2</sub>O<sub>3</sub> gate dielectrics by evaporation of Al films with a shadow mask during evaporation and then oxidized in nitric acid, a shadow mask with a tilt angle with respect to the horizontal wafer is placed in front of the wafer during evaporation. The continuously varied Al thickness on a single wafer is obtained by this simple technique. The former proposed method of oxidation in nitric acid was used to oxidize the formed Al films to become Al<sub>2</sub>O<sub>3</sub>. This low temperature Al<sub>2</sub>O<sub>3</sub> high-k dielectrics are stable in reliability.

Keywords: High-*k* dielectrics, HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, strain-anodization.

#### 二、緣由與目的:

在顯示器或軟性基板上,有許多製程是需要在低溫下進行的,由於溫度低,所以絕緣層之品質改善倍受注意,如何有效改善漏電流或提高可靠度,相關技術是值得注意的。本計畫所度提出要得到低溫絕緣層,可將薄金屬層予以液體酸中氧化,但必需金屬很薄;因此將晶圓於濺鍍設備中傾斜一角度,利用不同之視角因素調整,可得連續厚度分布之金屬膜層,再於之後的氧化步驟可得連續厚度分布之不同氧化層,這對元件特性分析是相當有用的。

另外,延續第一年之成果,發現若在 SiO<sub>2</sub> 與 Si 界面間給予適當之應力,則在氧化層生長時會有較完整之晶格結構,所得之氧化層特性 獲改善。在本年度中,同時研究 p 型及 n 型矽基板之應力陽極氧化生長氧化層,結果均發現在相同厚度下,MOS 元件之漏電流獲明顯改善,這對矽基板相關氧化層之低溫備製技術是有相當的助益。

在研究不同厚度之高介電絕緣層時,本單位亦發現在傳統之蒸鍍鋁金屬時,若將一遮罩置於晶圓之前,再給予適當之傾斜角度,可得不同厚度且連續變化之金屬鋁膜,之後再利用硝酸氧化法可得 Al<sub>2</sub>O<sub>3</sub>高介電常數絕緣層,由於均為低溫下完成,且在同一片晶圓上可以有多種厚度可供研究,可得知何種厚度配合最佳氧化製程可得最可行之絕緣層膜備製條件,相當具前瞻性。

#### 三、研究方法與成果:

#### (A).以傾斜晶圓濺鍍 Hf 金屬並以硝酸氧化再 純水補償備製低溫 HfO<sub>2</sub> 高介電常數絕緣 層技術

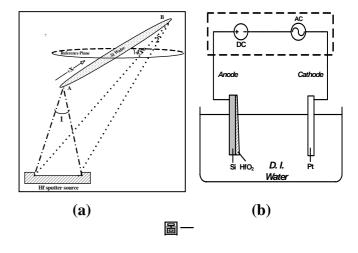

圖一(a)為一傾斜晶圓於濺鍍時之不同濺鍍視角示意圖,由於濺鍍源非點狀源,而是有一空間之分布,因此在晶圓上會形成不同之厚度。圖一(b)為陽極氧化槽示意圖,用來將氧化後之 HfO₂ 予以純水中修補漏電路徑。在陽極氧化補償後,元件會在 380°C 下於 N2 環境中進行退火,期使元件特性改善。

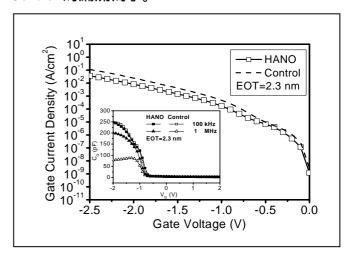

圖二為所得有經陽極氧化補償的 HfO<sub>2</sub>(簡稱 HANO)與對照組之 C-V 及 I-V 比較圖,可看出在相同等效厚度(EOT)為 2.3nm 下,HANO 較 Control 的漏流為小。

圖二

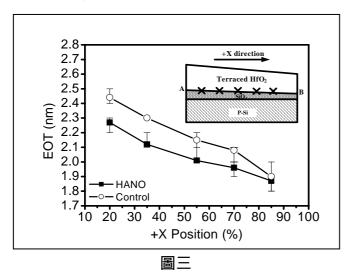

圖三為在同一晶圓上所量得之 HANO 與 Control 之 EOT 對位置分布圖,可看出 EOT 確 實隨位置而漸變,表示傾斜濺鍍確實發揮效果;同時可得知 HANO 較 Control 之 EOT 為小,表示 HANO 所得之 HfO2 較為理想,其介電常數值較大,因此 EOT 較小。

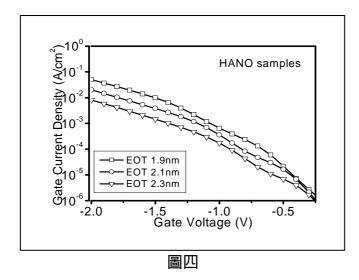

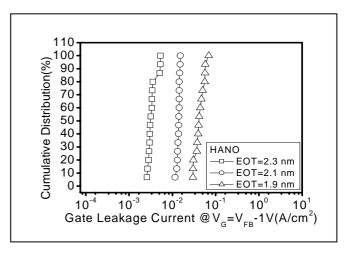

圖四為所得 HANO 元件在 EOT 為 1.9、2.1、及 2.3 nm 下之 I-V 特性,可看出電流會隨厚度而做變化,具高介電常數絕緣層之不同厚度特徵。

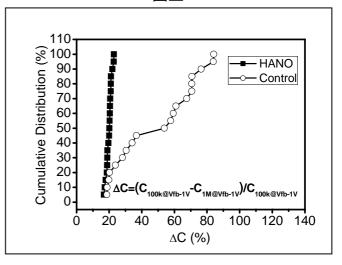

圖五為 HANO 元件在 EOT 為 1.9、2.1、及 2.3 nm 下在  $V_{G}=V_{FB}-1V$  下之電流密度累積統計分布圖 ,可看出電流分布相當均勻 ,較純  $SiO_2$  的漏電流為低 ,本 HANO 元件已充份展示出高介電常數絕緣層之特徵。圖六則為 C-V 曲線在聚集區(accumulation region)之電容在不同頻率下之變化量比較 ,可得知 HANO 較 Control 的電容隨頻率變化率為小 ,也就是說絕緣層之品質較佳 ,陽極氧化補償效果相當明顯有用。

圖五

圖六

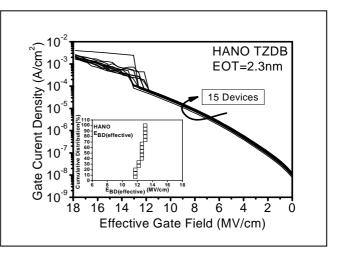

圖七為 EOT=2.3 nm 的元件其 I-V 特性,相當一致,而 TZDB 崩潰電場可高達 12MV/cm以上,充份顯示該低溫製程所得 HANO 絕緣層品質之優異。

圖七

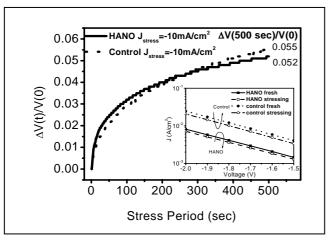

圖八為 HANO 與 Control 元件在定電流施加下之可靠度比較,可看出 HANO 之表現較為穩定。

圖八

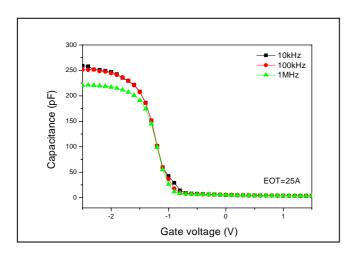

圖九為一EOT = 2.5 nm 的 HANO 元件不同 頻率下之 C-V 特性,可看出界面陷阱密度甚小,頻率引起之變化不大, $V_{FB}$  值亦接近理想值,可視為一絕佳的絕緣層。

圖九

#### (B). 以純水應力陽極氧化生長法備製高品質超 薄閘極氧化層技術

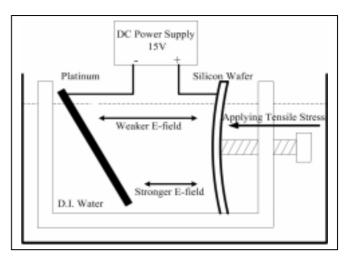

本計畫第一年即已提出如圖十所示之傾斜陽極氧化系統,將 Pt 陰電極予以傾斜,再進行陽極氧化可得不同厚度之氧化層於同一晶圓上,此外在晶圓背面施加一外應力,可使晶圓生長時承受伸張應力,因為在室溫下陽極氧化可有效控制生長速率,很適合超薄氧化層之生長,而伸張應力施加可改善氧化時之晶格距離之差異,因此可達到控制氧化層品質之目的。

圖十

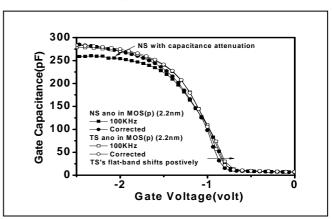

圖十一為以伸張力生長(TS)與對照組(NS) MOS(p)元件在同厚度為 2.2 nm 下之 100 KHz 與修正後 C-V 特性比較,可清楚看出 TS 元件之電容變化甚少,較 NS 元件表現為佳。

圖十一

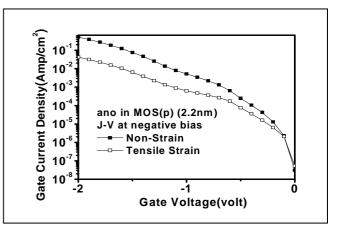

圖十二為圖十一兩元件之 J-V 特性比較,可清楚得知 TS 之漏電流明顯較 NS 為小,顯示氧化層之品質較佳。

圖十二

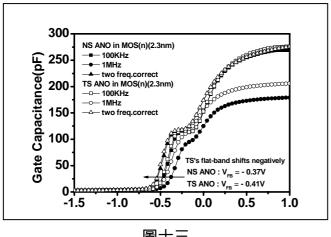

圖十三為以伸張力生長(TS)與對照組(NS) MOS(n)元件在同厚度為2.3 nm 下之1 MHz, 100 KHz 與修正後 C-V 特性比較,可清楚看出 TS 元件之電容變化較少,較 NS 元件表現為佳。

圖十三

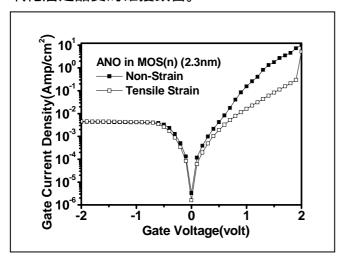

圖十四為圖十三兩元件之 J-V 特性比較, 可清楚得知 TS 之漏電流明顯較 NS 為小, 顯示 氧化層之品質的確獲改善。

圖十四

從上述之實驗觀察可得知,在超薄氧化層 生長時,若能在基板上給予適當之伸張力施 加,所得之氧化層因晶格較匹配之故,特性獲 明顯改善,此技術仍有相當大的研究空間,將 會持續進行並強調其應用性。

#### (C).以傾斜遮罩蒸鍍 AI 金屬並以硝酸氧化備 製低溫 Al<sub>2</sub>O<sub>3</sub> 高介電常數絕緣層技術

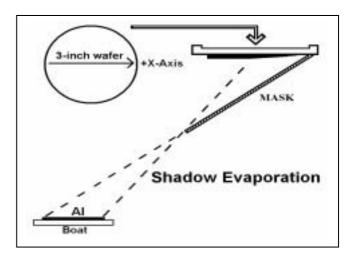

在備製超薄高介電常數絕緣層時,若是經 由氧化金屬得到絕緣層,則事先之金屬膜需愈 薄愈好,但因蒸鍍金屬需兼顧蒸鍍速率及時 間,才能得到甚薄之金屬,相當不易。本研究 提出有別於(A)部份所提之方法,於傳統蒸鍍金 屬鋁時,另加一遮板如圖十五所示,利用遮板 形成不同之視角因素(view factor),可得不同厚 度之金屬膜於同一晶圓上,而且可得甚薄之金 屬膜以供超薄高介電常數絕緣膜備製用。

圖十五

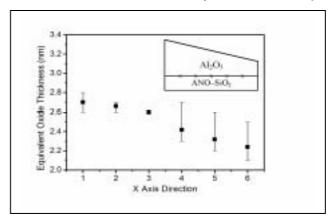

圖十六為將漸變厚度金屬鋁經硝酸氧化 後,並經低溫 400°C 於 N2 下退火 10 minutes 所得之 MOS(p)元件等效厚度(EOT)分布圖,可 看出 EOT 的確隨位置而漸變,如上述之預測。

圖十六

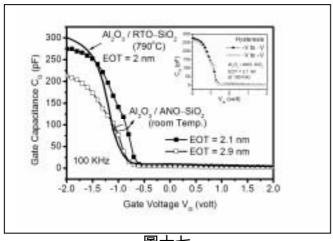

圖十七為低溫製程所得Al2O3/ANO-SiO2堆 疊結構 MOS(p)元件於 2.1 及 2.9 nm 下之 C-V 特性,同時高溫之Al<sub>2</sub>O<sub>3</sub>/RTO-SiO<sub>2</sub>於2nm下 之 MOS(p) C-V 曲線亦做為比較,可得知低溫之 Al<sub>2</sub>O<sub>3</sub>/ANO-SiO<sub>2</sub> 具有較多之負電荷,但絕緣層 之基本特徵均在,其遲滯現象亦不大,如內插 圖所示。

圖十七

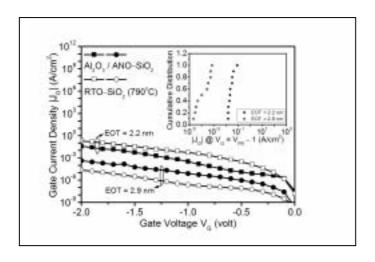

圖十八為上述元件之 J-V 特性圖,可看出對於 EOT=2.2~nm 的元件, $Al_2O_3/ANO-SiO_2$  較 RTO- $SiO_2$  具有較小之漏電流,顯示高介電常數絕緣層之特徵;但對 EOT=2.9~nm 則相反,這與金屬鉛被氧化之程度有關,若金屬鉛太厚,則氧化容易不完全,造成漏流嚴重。本研究顯示出可用遮板方式得到甚薄之金屬鋁膜,超薄且低溫製程之  $Al_2O_3$  高介電常數絕緣層是可預期的。

圖十八

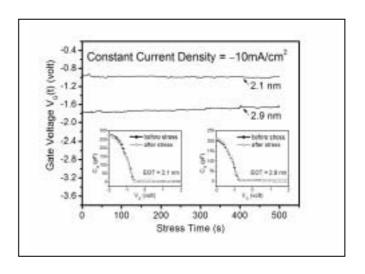

圖十九為  $Al_2O_3/ANO$ -SiO<sub>2</sub> 結構於 EOT=2.1 及 2.9 nm 下之定電流施加可靠度分析,可看出較薄之元件其穩定度較佳,而且經施加前後之 C-V 特性變化甚小,對低溫製程(<400°C)絕緣層而言,本方法是相當具參考性的,值得持續研究與改善。

圖十九

#### 四、總結與討論

在本計畫第二年度之研究中,主要提供了 二種具前瞻性之超薄膜層備製技術及延續第一 年開發之應力下生長高品質氧化層技術,發現 出利用傾斜晶圓濺鍍Hf金屬並以硝酸氧化再純 水補償可備製低溫 HfO2 高介電常數絕緣層,及 以傾斜遮罩蒸鍍 AI 金屬並以硝酸氧化可備製低 溫 Al<sub>2</sub>O<sub>3</sub> 高介電常數絕緣層, 兩項技術均具創意 及應用性;同時提出之以純水應力陽極氧化生 長法備製高品質超薄閘極氧化層技術,對超薄 氧化層備製法有其參考價質。所提出之技術均 為低溫製程,因此尚有許多的改善空間可做為 研究題材。所得成果已發表於 Applied Physics Letters 及整理投稿中,相信在後續的研究中會 將本計畫提出之技術給予更多之應用。主持人 在執行國科會研究計畫由2004年至今所產出之 研究成果表列如下,僅此提供參考。

# 五、主持人近三年半(2004~至今)之研究成果:(A) Refereed Paper

- 1. Z.H.Chen, S.W.Huang, and <u>J.G.Hwu</u>, 2004, "Electrical Characteristics of Ultra-thin Gate Oxides (<3nm) Prepared by Direct Current Superposed with Alternating-current Anodization", *Solid-State Electronics*, Vol.48, PP.23-28.

- 2. Y.P.Lin and <u>J.G.Hwu</u>, 2004, "Quality Improvement in LPCVD Silicon Nitrides by Anodic and Rapid Thermal Oxidations", *Electrochemical and Solid-State Letters*, Vol.7, No.5, PP.G87-G89.

- 3. W.J.Liao, Y.L.Yang, S.C.Chuang, and <u>J.G.Hwu</u>, 2004, "Growth-Then-Anodization Technique for Reliable Ultra-Thin Gate Oxides", *Journal of The*

- Electrochemical Society, Vol.151, No.9, G549-G553.

- C.S.Kuo, J.F.Hsu, S.W.Huang, L.S.Lee, M.J.Tsai, and J.G.Hwu, 2004, "High-k Al<sub>2</sub>O<sub>3</sub> Gate Dielectrics Prepared by Oxidation of Aluminum Film in Nitric Acid Followed by High Temperature Annealing", *IEEE Transactions on Electron Devices*, Vol.51, No.6, June, Vol.51, No.6, June 2004, PP.854-858.

- 5. Y.P.Lin and <u>J.G.Hwu</u>, 2004, "Oxide Thickness Dependent Suboxide Width and Its Effect on Inversion Tunneling Current", *Journal of The Electrochemical Society*, Vol.151, No.12, G853-G857.

- Y.H.Shih, S.R.Lin, T.M.Wang, and J.G.Hwu, 2004, "High Sensitive and Wide Detecting Range MOS Tunneling Temperature Sensors for On-Chip Temperature Detection", *IEEE Transactions on Electron Devices*, Vol.51, No.9, September 2004, PP.1514-1521.

- Y.P. Lin and J.G.Hwu, 2004, "Suboxide Characteristics in Ultrathin Oxides Grown under Novel Oxidation Processes", *Journal of Vacuum Science and Technology* A, Nov/Dec, PP.2265-2272.

- 8. Y.L.Yang and <u>J.G.Hwu</u>, 2004, "Quality Improvement of Ultra-Thin Gate Oxide by Using Thermal-Growth Followed by Scanning-Frequency Anodization (SF ANO) Technique", *IEEE Electron Device Letters*, Vol.25, No.10, October 2004, PP.687-689.

- S.W.Huang and J.G.Hwu, 2004, "Ultra-Thin Aluminum Oxide Gate Dielectric on N-Type 4H-SiC Prepared by Low Thermal Budget Nitric Acid Oxidation", *IEEE Transactions on Electron Devices*, Vol.51, No.11, PP.1877-1882.

- T.M. Wang and <u>J.G. Hwu</u>, 2005, "Temperature-Induced Voltage Drop Rearrangement and Its Effect on Oxide Breakdown in MOS Capacitor Structure", *Journal of Applied Physics*, Vol.97, No.4, PP.044504-1~044504-5.

- 11. C.H.Chang, T.M. Wang, and J.G.Hwu\*, 2006, "Quality Improvement and Electrical characteristics of High-k Films after Receiving Direct Superimposed with Alternative Current Anodic Oxidation (DAC-ANO) Compensation", Electrochemical Society Transactions Physics and Technology of High-k Gate Dielectric III, Volume 1, Issue 5, PP. 465-475. (EI)

- S.W.Huang and J.G.Hwu\*, 2006, "Indication of Lateral Nonuniformity of Effective Oxide Charges in High-k Gate Dielectrics by Terman's Method", *Electrochemical* Society Transactions - Physics and Technology of High-k Gate Dielectric III, Volume 1, Issue 5, PP.789-796. (EI)

- 13. C.J.Hung and <u>J.G.Hwu</u>\*, 2006, "Enhancement in Ultra-thin Oxide Growth by Thermal Induced Tensile Stress", *IEEE Transactions on Device and Material Reliability*, Vol.6, No.1, PP.28-32. (SCI/EI)

- 14. S.W.Huang and <u>J.G.Hwu</u>\*, 2006, "Lateral Nonuniformity of Effective Oxide Charges in MOS Capacitors with Al<sub>2</sub>O<sub>3</sub> Gate Dielectrics", *IEEE Transactions on Electron Devices*, Vol.53, No.7, July, PP.1608-1614. (SCI/EI)

- 15. C.W.Tung, Y.L.Yang and <u>J.G.Hwu</u>\*, 2006, "Impact of Strain-Temperature Stress on Ultrathin Oxide", *IEEE Transactions on Electron Devices*, Vol.53, No.7, July, PP.1736-1737. (SCI/EI)

- T.M.Wang, C.H.Chang, and <u>J.G.Hwu</u>\*, 2006, "Enhancement of Temperature Sensitivity of Metal-Oxide-Semiconductor (MOS) Tunneling Temperature

- Sensors by Utilizing Hafnium Oxide (HfO<sub>2</sub>) Film Added on Silicon Dioxide (SiO<sub>2</sub>)", *IEEE Sensors Journal*, Vol. 6, No. 6, December, PP. 1468-1472. (SCI)

- 17. T.M.Wang, C.H.Chang, S.J.Chang, and <u>J.G.Hwu</u>\*, 2006, "Comparison of Saturation Current Characteristics for Ultra-thin Silicon Oxides Grown on N- and P-type Silicon Substrates Simultaneously", *Journal of Vacuum Science and Technology A*, Vol. 24, No.6, November/December, PP.2049-2053. (SCI/EI)

- 18. K.C.Chuang and J.G.Hwu\*, 2006, "Improvement in Electrical Characteristics of High-*k* Al<sub>2</sub>O<sub>3</sub> Gate Dielectric by Field-Assisted Nitric Oxidation", *Applied Physics Letters*, Vol.89, No.23, December, PP.232903-1~232903-3. (SCI/EI)

- 19. J.C.Tseng and <u>J.G.Hwu</u>\*, 2007, "Effects of Electrostatic Discharge (ESD) High-Field Current Impulse on Oxide Breakdown", *Journal of Applied Physics*, Vol.101, No.1, January, PP. 014103-1~014103-6. (SCI/EI)

- 20. J.C.Chiang and J.G.Hwu\*, 2007, "Low Temperature (< 400 ) Al<sub>2</sub>O<sub>3</sub> Ultrathin Gate Dielectrics Prepared by Shadow Evaporation of Aluminum Followed by Nitric Acid Oxidation", *Applied Physics Letters*, Vol.90, No.10, March, PP.102902-1~102902-3. (SCI/EI)

- Y.L.Yang, C.H.Chang, Y.H.Shih, K.Y.Hsieh, and <u>J.G.Hwu</u>\*, 2007, "Modeling and Characterization of Hydrogen Induced Charge Loss in Nitride Trapping Memory", *IEEE Transactions on Electron Devices*, June (SCI/EI) (accepted)

- 22. J.C.Tseng and <u>J.G.Hwu</u>\*, 2007, "Oxide Trapped Charges Induced by Electrostatic Discharge (ESD) Impulse Stress", *IEEE Transactions on Electron Devices*, (SCI/EI) (accepted)

#### (B) Conference Paper

- C.S.Kuo, L.S.Lee, M.J.Tsai, and J.G.Hwu, 2004, "Ultra-thin HfO2 Gate Dielectrics Prepared by Oxidation of Hf Metal Film in Nitric Acid Followed by High Temperature Anneal", *International Symposium on Nanoelectronic Circuits and Giga-scale Systems* (ISNCGS 2004), February 12-13, Miao-Li, Taiwan, PP.51-55.

- 2. Y.P.Lin and J.G.Hwu, 2004, "MOS Tunneling Diodes with Ultra-thin Oxides of N-type and P-type Silicon Substrates", *International Symposium on Nanoelectronic Circuits and Giga-scale Systems (ISNCGS 2004)*, February 12-13, Miao-Li, Taiwan, PP.56-60.

- 3. S.W.Huang, H.L Tsai, J.R. Yang, C.W.Hsu, C.W.Hsiung, and J.G.Hwu, 2004, "Alternative Nano-Scale Gate Dielectric on 4H-SiC Prepared by Low Thermal Budget Nitric Acid Oxidation of Ultra-thin Aluminum Film", *International Symposium on Nanoelectronic Circuits and Giga-scale Systems (ISNCGS 2004)*, February 12-13, Miao-Li, Taiwan, PP.35-39.

- 4. <u>J.G. Hwu</u>, 2004, "Thin Gate Dielectrics Process and Application", *IMEC-Taiwan NSC Workshop on Nanotechnology on the occasion of IMEC's* 20<sup>th</sup> *Anniversary*, September 24, Leuven, Belgium. (invited)

- T.M. Wang and J.G. Hwu, 2004, "Temperature-Induced Voltage Drop Rearrangement and Its Effect on Oxide Breakdown in MOS Capacitor Structure", Proceedings of Electronic Devices and Materials Symposium, December 20-23, Shin-Chu, Taiwan, Republic of China,

- 319-322.

- C.H. Chang, L.S. Lee, M.J. Tsai, and <u>J.G. Hwu</u>, 2004, "Electrical characteristics of high-k HfO<sub>2</sub> gate dielectrics prepared by oxidation in HNO<sub>3</sub> followed by rapid thermal annealing in N<sub>2</sub>", *Proceedings of Electronic Devices and Materials Symposium*, December 20-23, Shin-Chu, Taiwan, Republic of China, PP.95-98.

- C.H. Chang, T.M. Wang, and J.G. Hwu, 2005, "Quality Improvement and Electrical characteristics of High-k Films after Receiving Direct Superimposed with Alternative Current Anodic Oxidation (DAC-ANO) Compensation", Sacramento, Level 2 in the Symposium "G3: High Dielectric Constant Gate Stacks III", Section: High-k Materials and Proceeding III, 208th Meeting of The Electrochemical Society, October 16-21, Westin Bonaventure, Los Angeles, California, USA, Paper No.550.

- 8. S.W. Huang and J.G. Hwu, 2005, "Indication of Lateral Nonuniformity of Effective Oxide Charges in High-k Gate Dielectrics by Terman's Method", Sacramento, Level 2 in the Symposium "G3: High Dielectric Constant Gate Stacks III", Section: Electrical And Reliability Characterization III, 208th Meeting of The Electrochemical Society, October 16-21, Westin Bonaventure, Los Angeles, California, USA, Paper No.577.

- 9. J.G. Hwu, 2005, "Process and Application of Silicon MOS Structures with Ultra-Thin Gate Dielectrics", Scotland-Taiwan Hi-Tech Forum: Micronanotechnology Workshop, October 12, The Royal Society of Edinburgh, Edinburgh, Scotland (invited)

- T.M. Wang, S.J. Chang and J.G. Hwu, 2005, "Comparison of Suboxide Characteristics for Ultra-thin Silicon Oxides Grown on N- and P-type Substrates Simultaneously", Proceedings of Electronic Devices and Materials Symposium, November 24-25, I-Shou University, Kaohsiung, Taiwan, Republic of China, Paper No.CO15.

- 11. T.H. Li and J.G. Hwu, 2005, "Reduction in Leakage Current in Ultra-thin Gate Oxides by Tensile-Stress Anodization", *Proceedings of Electronic Devices and Materials Symposium*, November 24-25, I-Shou University, Kaohsiung, Taiwan, Republic of China, Paper No.CO17.

- 12. H.P. Lin and J.G. Hwu, 2005, "Direct Observation of the Lateral Nonuniformities of Charges in the Dielectric Layer of MOS Capacitors by Terman Method", Proceedings of Electronic Devices and Materials Symposium, November 24-25, I-Shou University, Kaohsiung, Taiwan, Republic of China, Paper No. AO05.

- 13. C.H. Chang and J.G. Hwu, 2005, "Application of the Direct Superimposed with Alternative Current Anodic Oxidation (DAC-ANO) Compensation Technique to Improve the Quality and Electrical Characteristics of Devices with High-k Gate Dielectrics", *Proceedings of Electronic Devices and Materials Symposium*, November 24-25, I-Shou University, Kaohsiung, Taiwan, Republic of China, Paper No. CO13.

- 14. K.C.Chuang and <u>J.G.Hwu</u>\*, 2006, "Electrical Characteristics of Silicon Oxide Film Grown by Anodic Oxidation in Nitric Acid at Low Temperature",

- Proceedings of International Electronic Devices and Materials Symposium, December 7-8, National Cheng-Kung University, Tainan, Taiwan, Republic of China, Vol. B & C, PP.112-113.

- 15. C.H.Chang, and J.G.Hwu\*, 2006, "Anodic Oxidation (ANO) Compensation Effect on The Leakage Reduction of Low Temperature High-k Al<sub>2</sub>O<sub>3</sub> Dielectrics as Prepared byTilted Evaporation of Aluminum Followed by Nitric Acid Oxidation", Proceedings of International Electronic Devices and Materials Symposium, December 7-8, National Cheng-Kung University, Tainan, Taiwan, Republic of China, Vol. A & D, PP.252-253.

- 16. H.P.Lin and J.G.Hwu\*, 2006, "Using QM-based Terman method as a direct index of the Lateral Nonuniformities of Charges in the Dielectric Layer of MOS Capacitors", Proceedings of International Electronic Devices and Materials Symposium, December 7-8, National Cheng-Kung University, Tainan, Taiwan, Republic of China, Vol. A & D, PP.297-298.

- 17. Y.L.Yang, C.H.Chang, Y.H.Shih, K.Y.Hsieh, and J.G.Hwu\*, 2006, "Hydrogen Eraser for Tightening V<sub>T</sub> Distribution of Nitride Trapping Memory", *Proceedings of International Electronic Devices and Materials Symposium*, December 7-8, National Cheng-Kung University, Tainan, Taiwan, Republic of China, Vol. A & D, PP.303-304.

- 18. P.K.Chang, and J.G.Hwu\*, 2006, "Ultrathin Gate Oxide Thickness (< 2.0 nm) Extraction Technique Based on Low Dissipation Factor Regions of MOS C V Curves", Proceedings of International Electronic Devices and Materials Symposium, December 7-8, National Cheng-Kung University, Tainan, Taiwan, Republic of China, Vol. A & D, PP.42-45. (invited)</p>

- J.G. Hwu\*, 2006, "Silicon MOS Structures with Ultra-Thin Gate Dielectrics", The Conference on the Micro/Nano Technology between Taiwan and Scotland, December 13, National Formosa University, Fu-Wei, Yun-Lin, Taiwan, PP.22-30. (invited)

#### (C) Technical Report

- 1. <u>J.G.Hwu</u>, May 2004, "Study on The Oxide Uniformity and Stress Effect in Rapid Thermal Processing (2/3)", *National Science Council*, NSC92-2215-E-002-005

- J.G.Hwu, July 2004, "Development of Si Novel Devices and Module Technology (3/3)", National Science Council, NSC92-2120-E-002-004

- 3. <u>J.G.Hwu</u>, July 2004, "Application of Ultra-thin Film Oxidation Technology on Si Devices (3/3)", *National Science Council*, NSC92-2120-E-002-005.

- 4. <u>胡振國</u>、 劉致為、吳又麟、林彥伯、黃思維、王宗苗、楊宜霖、郭智昇、張嘉華、陳自強、李秋宗、詹孫戎、魏潔瑩、陳博文, 2004, "矽新型元件及模組技術研發(3/3)", 奈米國家型科技計畫成果發表會暨台灣 奈米科技展, September 6~8, Taipei, Taiwan, DE-2-6, PP.340~348.

- J.G.Hwu, May 2004, "Process Development of Ultra-thin Gate Dielectrics and Novel Device Applications of Silicon MOS Structure (1/3)", National Science Council, NSC93-2215-E-002-016

- 6. <u>J.G.Hwu</u>, May 2005, "Process Development of Ultra-thin Gate Dielectrics and Novel Device Applications of Silicon MOS Structure (1/3)", *National*

- Science Council, NSC93-2215-E-002-016

- 7. <u>J.G.Hwu</u>, August 2005, "Study on The Oxide Uniformity and Stress Effect in Rapid Thermal Processing (3/3)", *National Science Council*, NSC93-2215-E-002-001.

- 8. <u>J.G.Hwu</u>, May 2005, "Process Development of Ultra-thin Gate Dielectrics and Novel Device Applications of Silicon MOS Structure (1/3)", *National Science Council*, NSC93-2215-E-002-016.

- 9. <u>J.G.Hwu</u>, August 2005, "Study on the Oxide Uniformity and Stress Effect in Rapid Thermal Processing (3/3)", *National Science Council*, NSC93-2215-E-002-001.

- J.G.Hwu, May 2006, "Process Development of Ultra-thin Gate Dielectrics and Novel Device Applications of Silicon MOS Structure (2/3)", National Science Council, NSC94-2215-E-002-004.

- 11. <u>J.G.Hwu</u>, May 2006, "Study of Advanced CMOS Devices and Processes (1/3)", *National Science Council*, NSC94-2215-E-002-047.

- 12. <u>J.G.Hwu</u>, May 2006, "Technologies of Forming High Quality Insulating Films for Low Substrate Temperature Process (1/3)", *National Science Council*, NSC94-2215-E-002-044.

- 13. <u>J.G.Hwu</u>, September 2006, "Research and Development of Micro Electronics Division (1/3)", *National Science Council*, NSC94-2217-E-002-016.

#### (D)Patent

- 1. <u>Jenn-Gwo Hwu</u>, Yen-Po Lin, and Szu-Wei Huang, "High-k Gate Dielectrics Prepared by Liquid Phase Anodic Oxidation", (*U.S.A. Patent* —Issued / Filed Dates –May 3, 2005 / July 17, 2002, Application No.-10/196380, Patent No.-6887310 B2, Duration-2002/7/17~2022/7/17)

- 李隆盛,曾培哲,郭智昇,胡振國,"金氧半電晶體之高介電值閘極介電層的製造方法",(中華民國專利 公告號-I228780,卷/期-032/007,申請案號-093101551,公告日期-20050301,證書號-發明第I228789號)

- 3. <u>胡振國</u>, 郭智昇, 黃思維, "利用硝酸氧化技術製造金屬氧化層之方法", (*中華民國專利* 申請案號 -092135307, 公告日期-20050521, 證書號-發明第 I232893號, 專利期限-2005/05/21~2023/12/11)

- 4. Lurng-Shehng Lee, Pei-Jer Tzeng, Chih-Sheng Kuo, and Jenn-Gwo Hwu, "Process of Forming High-K Gate Dielectric Layer for Metal Oxide Semiconductor Transistor", (U.S.A. Patent —Issued / Filed Dates –January 31, 2006 / May 5, 2004, Application No.-10/838343, Patent No.- 6991989 B2, Duration-2004/5/5~2024/5/5)

# 可供推廣之研發成果資料表(一)

| 可申請專利    | 可技術移轉                                                                                                                                                                                      | 日期: <u>96</u> 年 <u>5</u> 月 <u>25</u> 日                                  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

|          | 計畫名稱:適用於低溫基板製程之高品質絕緣膜形成技術(2/3)                                                                                                                                                             |                                                                         |

| 國科會補助計畫  | 計畫主持人:胡 振 國                                                                                                                                                                                |                                                                         |

|          | 計畫編號:NSC95-2221-E-002-358                                                                                                                                                                  | 學門領域:微電子                                                                |

| 技術/創作名稱  | 以傾斜晶圓及加遮罩技術備製超薄低                                                                                                                                                                           | 溫高介電常數絕緣層                                                               |

| 發明人/創作人  | 胡振國 江榮進 張嘉華                                                                                                                                                                                |                                                                         |

| 技術說明     | 中文:     提出之傾斜晶圓及加遮罩技術,可製程可得超薄品質佳之高介電常數絕類  英文:     Novel technology of using tilte prepare ultra-thin metal films is potultra-thin low temperature high-k diele low in process temperature. | 緣層,成本低,甚具應用性。 ed wafer and adding mask to ential for the preparation of |

| 可利用之產業及  | 1. 先進低溫製程高品質絕緣層<br>2. 低溫大面板絕緣層品質改善                                                                                                                                                         |                                                                         |

| 可開發之產品   |                                                                                                                                                                                            |                                                                         |

| 技術特點     | <ol> <li>低成本</li> <li>可在同一基板上備製不同厚度絕經</li> <li>具超薄高介電常數絕緣層之開發</li> <li>低溫處理不易引起雜質重分布</li> </ol>                                                                                            |                                                                         |

| 推廣及運用的價值 | <ol> <li>現今低溫製程廣受重視,高品質約<br/>取得先機,商機無限。</li> <li>研發成本低,相對風險低,值得</li> </ol>                                                                                                                 |                                                                         |