# 行政院國家科學委員會補助專題研究計畫成果報告

**\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\***

計畫名稱:新穎光電材料與奈米結構元件之研究 (2/2)

※ 子計畫二: 氮化鎵製程與模擬:光致氧化膜之光電應用※

計畫類別:整合型計畫

計畫編號: NSC 90-2215-E-002-023

執行期間:90年8月1日至91年7月31日

計畫主持人: 彭隆瀚

計畫參與人員:巫漢敏, 石清文

執行單位:台灣大學光電所

中華民國91年10月25日

## Photo-oxidation process of Ga<sub>2</sub>O<sub>3</sub>/GaN MOS devices

## L.-H. Peng

Department of Electrical Engineering and Institute of Electro-Optical Engineering

National Taiwan University, Taipei, 106 Taiwan, R.O.C.

Tel: 886-2-2363-5251 x 408; Fax: 886-2-2367-7467; email: peng@cc.ee.ntu.edu.tw

**Abstract:** We report the use of photo-enhanced wet oxidation process on GaN-based metal-oxide-semiconductor (MOS) devices. From the I-V measurements of the GaN-MOS, the breakdown field strength was found to be 0.5 MV/cm. The high frequency capacitance-voltage and conductance measurements revealed the interface-state density was in the range of  $10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup>.

#### 1.Introduction

Gallium nitride has been regarded as an excellent candidate for the high-power and high frequency transistors operating at elevated temperatures, due to its wide bandgap, high electron saturation velocity, and high breakdown electrical field. Therefore the development of GaN-based transistors, including MESFETs, HEMTs, and HFETs [1]-[3] had attracted much attention, and had rapid progress in recent years. However, the excessive electrical field in the GaN substrate, surface polarization charges, and leakage current through the gate would induce the current collapse effect and limit the power-handling capabilities of these devices. Moreover when temperature raises, the gate leakage current becomes even larger, it would seriously degrade the transistor performance. By using an insulating and passivating layer under the gate electrode, it is possible to lower the gate leakage current, excessive electrical field, and surface polarization charges and to improve the device characteristics. A number of studies of the GaN metal-insulating-semiconductor (MIS) structure have been made by employing Ta<sub>2</sub>O<sub>5</sub>, SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, and Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>) as gate insulators [4]-[6]. But these reports have revealed unsatisfactory results either through high leakage currents or high density of interface state. The main reason can be ascribed to less developed oxidation process on GaN.

In this report, we present the characteristics of Ga<sub>2</sub>O<sub>3</sub>/GaN MOS by employing a photoelectrical chemical process [7] to grow the native oxide layer Ga<sub>2</sub>O<sub>3</sub> on GaN. The high frequency capacitance-voltage (C-V) and current-voltage (I-V) measurements had been taken and interface-state density was calculated by using Terman's method and conductance me as ure ments technology.

## 2. Experimental

The Si-doped n-type GaN epilayers used for this report were grown on sapphire substrates by metalorganic chemical vapor deposition (MOCVD). The doping concentration and mobility are 1.3 x 10<sup>17</sup> cm<sup>-3</sup> and 460 cm<sup>2</sup>/Vs, respectively.

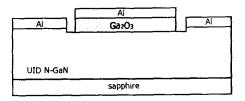

The native Ga<sub>2</sub>O<sub>3</sub> layer was grown by the PEC oxidation method at room temperature. After growth, the sample was heated up to 400°C for 1 hour to remove the H<sub>2</sub>O molecules and strengthen the Ga<sub>2</sub>O<sub>3</sub> molecular structure. The thickness of oxide layer was measured to be about 180nm by surface profiler. The metal gate and contact electrodes to the GaN substrate were made by thermal deposition of 100nm alurninum. Through standard lithography and etching process, the PEC-grown Ga<sub>2</sub>O<sub>3</sub>/GaN MOS device with area 1.767×10<sup>-4</sup> cm<sup>-2</sup> was fabricated.

Fig.1 The side-view profile of GaN MOS.

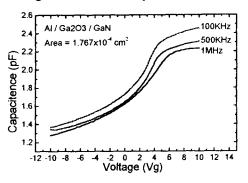

Fig. 2 CV response of Ga<sub>2</sub>O<sub>3</sub>/GaN MOS

The C-V, and G-V characteristics were taken in a shielding box at room temperature using a parallel circuit model with a HP 4284 LCR meter. The I-V measurement was carried out by using a Keithley model K238 current source.

## 3. Results and discussion

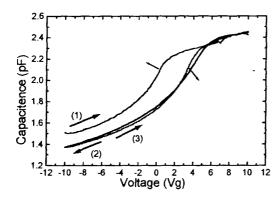

Fig. 3 The C-V traces under 1MHz with biasing

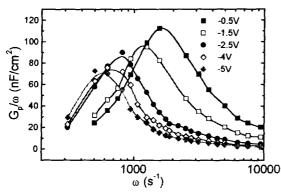

Fig. 4 The  $G_p/\omega$  curves at different bias value in the depletion region of a GaN MOS capacitor.

The C-V measurements for a Ga<sub>2</sub>O<sub>3</sub> film 180nm-thick as grew on GaN, shown in Fig. 2, indicate a transition between accumulation and depletion, and minor shift in the flatband voltage with various frequencies. Instead of inversion, deep depletion can be reached under negative biasing voltage, indicating the generation rate of minority carriers near the surface is not sufficient to from an inversion layer. The increasing in capacitance at the accumulation with decreasing frequency is caused by the series resistance attributed to the not-perfect ohmic contact and GaN semiconductor resistance.

In Fig. 3, the C-V measurements with biasing voltages sweeping up and down show a capacitance hysteresis, and indicate there are oxide traps within the Ga<sub>2</sub>O<sub>3</sub> film. In the first time sweeping up to accumulation, the oxide traps catch the negative charges to become oxide-trapped charges. More positive voltage is necessary to be applied to compensate the

negative oxide-trapped charges; therefore about 3V shift in curves is observed in the followed C-V sweeping measurements. From the curve-shift, the density of the oxide traps could be calculated to be  $2.6 \times 10^{11} \text{cm}^{-2}$

In the studies of MOS capacitor, interface-state density is one of the most important parameters to confirm the quality of the interface between oxide and semiconductor layer. The most often used technology to measure the density is the Terman's method. But Terman's method grossly underestimates the actual interface-state density. Therefore we the ac-conductance measurement technology to more accurately probe the interface-state density [8]. The interface-state density is determined from the peak  $G_p/\omega$  value, and each value of applied gate bias is converted into a surface potential corresponding to the femi-level position within the bandgap.

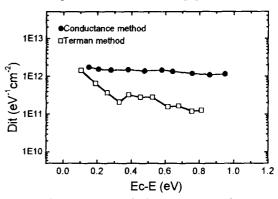

Fig. 5 Derived values of Dit as a function of energy obtained from Terman's and ac-conductance method for GaN MOS

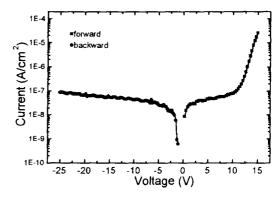

Fig. 6 gate-leakage current density vs bias voltages

From the curves in Fig. 5, we are able to observe the derived values of Dit as a function of energy obtained from Terman's and ac-conductance method. As predicted, the density of Dit derived by Terman's method is smaller than that derived by ac-conductance measurement. After comparison, we can conclude the interface-state density of the

$Ga_2O_3/GaN$  MOS is in the range of  $10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup>, and the best result is  $1.3 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup>

The I-V measurements on the  $Ga_2O_3/GaN$  MOS in Fig. 6 show leakage current density in the range of  $10^{-7}$ - $10^{-9}$  A/cm<sup>2</sup>, which is quite small, even at large negative biasing voltage. The derived breakdown field strength of the  $Ga_2O_3$  oxide is about 0.5 MV/cm.

#### 4. Conclusion

Instead of ordinary deposited insulating layer, we employed the photoelectrical chemical process to grow the native oxide  $Ga_2O_3$  of ,GaN to be the insulating-oxide layer for MOS capacitor. We performed the Terman's and ac-conductance method to measure the interface-state density on GaN MOS capacitor. Our result shows the Dit to be in the range of  $10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup>, and the best result is  $1.3 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup>. In addition, we examined both the leakage current and breakdown field strength, the result shows the leakage current density is quite small even at large negative biasing voltage, and the breakdown field strength of the  $Ga_2O_3$  oxide is about 0.5 MV/cm

#### 5. References

[1] W. S. Lee, et al, "high temperature

performance of recessed gate GaN MESFETs fabricated using photoelectrochemical etching process", Electronics letters, vol. 36, pp. 265, 2000

[2] B. Luo, et al, "dc and rf performance of proton-irradiated AlGaN/GaN high electron mobility transistors". Applied physics letters, vol. 79, pp. 2196, 2001.

[3] X. Hu, et al,

"Si<sub>3</sub>N<sub>4</sub>/AlGaN/GaN-metal-insulator-semiconduc tor heterostructure field-effect transistors". Applied physics letters, vol. 79, pp. 2832, 2001.

[4] L. W. Tu, et al, "high-dielectric-constant Ta<sub>2</sub>O<sub>5</sub>/n-GaN metal-oxide-semiconductor structure", Applied physics letters, vol. 77, pp. 3788, 2000.

[5] S. Arulkumaran, et al, "investigations of SiO<sub>2</sub>/n-GaN and Si<sub>3</sub>N<sub>4</sub>/n-GaN insulator-semiconductor interfaces with low interface state density", Applied physics letters, vol. 73, pp. 809, 1998.

[6] M. Hong, et al, "Properties of  $Ga_2O_3(Gd_2O_3)/GaN$  metal-insulator-semiconductor diodes", J. Vac Sci. Technol. B 18, pp. 1453, 2000.

[7] L. H. Peng, et al, "photoenhanced wet oxidation of Gallium nitride", Applied physics letters, vol. 76, pp. 511, 2000.

[8] MOS Physics and Technology, by E. H. Nicollian and J. R. Brew