# 行政院國家委員會電信國家型科技研究計畫成果報告

K-頻段無線收發關鍵元組件之研究(1/3)(2/3)(3/3)-子計畫四:

頻率倍頻器之研製(1/3) (2/3) (3/3), Study of Frequency Multiplier (1/3) (2/3) (3/3)

計畫編號: NSC88-2219-E-002-014, NSC88-2219-E-002-019, NSC90-2219-E-002-043

執行期限:87年8月1日至90年7月31日

計畫主持人: 瞿大雄 教授 國立台灣大學電信工程學研究所

#### 一、摘要

本計畫旨在建立頻率倍頻器相關之理論分析、 模擬、製作與實驗量測。本報告係敘述三年之研究 成果,主要包含兩項,一為使用CIC之PML GaAs PHEMT MMIC製程,研製3至18 GHz六倍倍頻器模 組之設計、模擬及量測結果。該倍頻器模組包含一3 至6GHz二倍倍頻器、6至18GHz三倍倍頻器以及一 17至22GHz緩衝放大器。二為提出一新的自振倍頻 器設計之方法,並將應用於主動天線陣列。該自振 電路可達到較高之倍頻輸出功率。其電路係以 harmonic-balance方法分析,由量測結果顯示和模擬 結果相當吻合。所研製之主動式倍頻天線陣列,顯 示經由改變個別振盪器之自由振盪頻率,可達成天 線場型掃瞄的效果。

關鍵字:倍頻器,自振倍頻器,主動天線陣列。 英文摘要

The purpose of this three-year research project is to the basic theory, numerical implementation and experimental measurement of frequency multiplier circuits. In this report, two major items are covered. One is the design, simulation and measurement results of a k-band PHEMT MMIC frequency multiplier using CIC PML GaAs foundry. The second result is to develop a new analysis method for a coupled active multiplier antenna array. This method harmonic-balance method and weakly couple oscillator dynamic theory to give a well prediction of the second harmonic output power, locking bandwidth, matching condition and phase distribution between array elements. An X-band active multiplier antenna array is fabricated and its measurement results shown in good agreement with simulation results.

Key words: multiplier, self-oscillating multiplier, active antenna array.

#### 二、計畫緣由及目的

無線收發機中,本地振盪器之相位調變雜訊和 頻率調變雜訊,對信號品質影響甚巨,尤其是在毫 米波段中。因此設計上多採用較低頻之頻率合成 器,再經多級倍頻器,以達到較高之工作頻率。

本報告主要敘述兩項研究成果,一為以HEMT 電晶體作為非線性元件及放大元件,設計主動式倍頻器。二為以自振倍頻器架構,設計主動式倍頻天線陣列。主動式倍頻器之優點為:(1)效率較被動式高,(2)需較低之輸入功率,(3)轉換損失較低。而自振倍頻器,則具有(1)較高之倍頻輸出功率,(2)較低之雜訊。

## 三、研究方法與成果

## 3.1 倍頻器模組

設計係使用 HP/Libra 軟體進行 HEMT 於直流偏壓點之線性與非線性特性,以及電路分析,MMIC 佈局以及設計法則檢驗則使用 Cadence 軟體。各相關之 MMIC 設計及實驗量測結果如下。

#### A. 二倍倍頻器

偏壓點選擇為 B 類放大器偏壓點,設計上選用 8 指(finger) 400 µ m HEMT 元件。匹配電路方面,輸出端設計上使用 LC 串聯共振器,以使其在共振頻率時,提供短路阻抗,最後輸出端則匹配至 50。輸入端係使用低通型式之匹配電路,以阻絕二倍頻出現於輸入端。

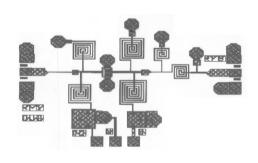

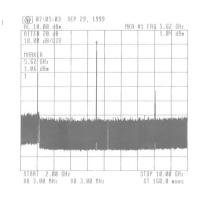

圖一為其之 MMIC 佈局圖。圖二為輸入功率為 10.84dBm 時,輸出功率之頻率響應,顯示輸出功率 約 0dBm~-5dBm, 因此轉換損失約為 10~15dB。圖 三為輸入功率 10.84dBm, 輸入頻率 2.81GHz 時, 其輸出頻譜, 顯示二倍頻對基頻拒斥比約 20dB, 對 三倍頻拒斥比則約 33dB。

#### B.三倍倍頻器

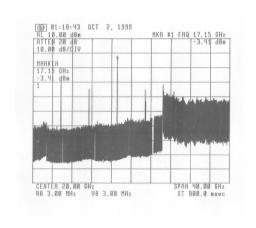

偏壓點選擇為 A 類放大器偏壓點,元件選擇 6 指 180 µ m 之 HEMT。匹配電路方面,輸出端使用 LC 串聯共振器,以在共振頻率時,提供短路阻抗。輸入端則使用低通型式匹配網路,以阻絕高次諧波出現至輸入端。圖四為 MMIC 佈局圖。圖五為量輸入功率為 10.61dBm 時,輸出功率之頻率響應,顯示輸出功率約 5dBm~-1dBm,因此轉換損失約為5~11dB。圖六為輸入功率為 10.61dBm 且輸入頻率為 5.71GHz 時,量得之輸出功率頻譜,顯示對基頻拒斥比約為 15dB,對二倍頻拒斥比約 20dB,對四倍頻拒斥比則約 23dB。

#### C.緩衝放大器

緩衝放大器設計選擇 A 類放大器偏壓點,同時使用損失匹配,以達到較佳之輸出端匹配。元件選擇 6 指 150 µ m HEMT 元件。圖七為 MMIC 佈局圖。圖八為量測之穿透係數(S21),該量測與模擬結果十分相近,穿透係數略低於模擬值應係由於量測時偏壓低於模擬之偏壓所致。

#### 3.2 主動式倍頻天線陣列

主動式倍頻天線陣列係由多個自振倍頻器組合,以下分別敘述其原理與量測結果。

#### A. 自振倍頻器

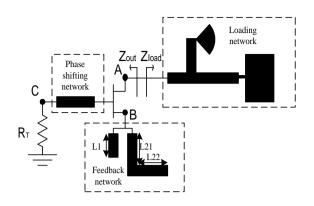

圖九為設計之自振倍頻器電路,其中傳輸線L1係用以提供陣振盪所須之負阻抗,L21及L22其長度約為振盪波長之 1/4,輸出端則設計為最佳二倍頻功率,因此天線不僅用以幅射二倍頻信號,並且做為匹配元件。其輸入端則外接注入信號,因此,工作時振盪器振盪於基頻,而可輸出最大之二倍頻信號,並經注入鎖定,達到高轉換效率與低雜訊。

電路分析係使用 harmonic balance 方法,並考慮適當之偏壓與阻抗匹配,以得到最佳之輸出功率。量測結果顯示與模擬相符,振盪頻率為 4GHz, 二倍頻輸出信號頻率為 8GHz,功率為 9.5dBm。

### B. 主動式倍頻天線陣列

圖十為設計之主動式倍頻天線陣列,包含三個 自振倍頻器電路,其分析則使用耦合振盪原理,以 計算各主動天線之輸出信號振幅與相位。當該主動 式倍頻天線陣列鎖定於注入信號時,可藉由調節各 自振倍頻器之振盪頻率,達到天線幅射場型之方位 角改變,圖十一為主動式倍頻天線陣列之幅射場型。 四、結論

由上節之敘述顯示,本計畫之主要研究成果包含兩項,一為研製3至18 GHz MMIC倍頻器,建立設計、模擬及量測能力。二為提出一新的主動式倍頻天線陣列架構與設計方法,其使用之自振倍頻器可達到較高之倍頻輸出功率。此主動式倍頻天線陣列不僅可應用於相位天線,亦可做為毫米波信號源之空間功率整合器。

### 五、圖表

圖一 二倍倍頻器佈局圖。

圖二 二倍倍頻器之輸出功率頻率響應量測結果。

圖三 二倍倍頻器輸出頻譜量測結果。

# 圖四 三倍倍頻器佈局圖。

## 圖五 三倍倍頻器之輸出功率頻率嚮應量測結果。

圖六 三倍倍頻器輸出頻譜量測結果。

圖七 緩衝放大器佈局圖。

圖八 衝放大器增益量測結果。