## 行政院國家科學委員會專題研究計畫 期中進度報告

## 具區塊記憶特性之隨機碼(2/3) 期中進度報告(精簡版)

計畫類別:個別型

計 畫 編 號 : NSC 95-2221-E-002-181-

執 行 期 間 : 95 年 08 月 01 日至 96 年 07 月 31 日 執 行 單 位 : 國立臺灣大學電機工程學系暨研究所

計畫主持人: 林茂昭

報 告 附 件 : 出席國際會議研究心得報告及發表論文

處 理 方 式 : 期中報告不提供公開查詢

中 華 民 國 96年05月17日

## 行政院國家科學委員會專題研究計畫 期中報告

具區塊記憶特性之隨機碼 (2/3)

Random Coding with InterBlock Memory

計畫編號: NSC 95-2221-E-002-181

執行期間:95年8月01日至96年10月31日 主持人:林茂昭 國立臺灣大學電機工程學系

### 一、中文摘要

在本年度計劃中,我們研究具區塊間記憶之渦輪碼編碼調變系統,其編碼架構為在傳統渦輪碼緩等統,其編碼架構為在傳統渦輪碼後串接一個多工器(multiplexer)、延遲處理器(delay processor)及訊號點對應器(signal mapper)。在本研究中,我們考慮相鄰區塊間之不同記憶程度,並為改善在單個的碼句(codeword)內反覆的解碼方法(IDSC)會導致大錯誤係數的問題,我們提出一種在相鄰碼句間訊息傳遞之重覆性解碼演算法(IDAC),可以提昇系統的可靠度。

研究成果顯示,在同樣的解碼複雜度、 錯誤率和解碼的延遲長度的考量下,我們所 設計的具區塊間記憶之渦輪碼編碼調變,在 使用 IDAC 來解碼下,不管是短碼或是長碼 均優於傳統的渦輪碼編碼調變系統。

關鍵詞:隨機碼、渦輪碼、編碼調變、重覆性解碼。

### 英文摘要

In this project, we investigate the performance of turbo coded modulation with interblock memory for which the encoding is implemented by serially concatenating a multiplexer, a multilevel delay processor, and a signal mapper to a conventional turbo encoder.

In this research, we consider the conditions of various degrees of interblock memory. We propose iterative decoding between adjacent codewords (IDAC), which provides error performance much better than the iterative decoding within a single codeword (IDSC). Simulation results show that with IDAC, turbo coded modulation with interblock memory is superior to the conventional turbo trellis coded modulation for either short or long code length

considering the associated complexity, error rates, and decoding delay.

Keywords: Random coding, Turbo Code, coded modulation, Iterative Decoding.

### 二、計畫的緣由、文獻探討與目的(Goals)

In the last decade, random-like codes such as binary turbo codes [1], low density parity check (LDPC) codes [2], turbo trellis coded modulation (TTCM) [3], and bit interleaved coded modulation (BICM) [4] have pushed the error performances of channel coding close to the Shannon limit for very long codes. However, there is still some room for improvement if the code lengths and coding complexity are taken into consideration.

Each of the turbo code, the LDPC code, or BICM is a block code for which the dependency of code bits (or symbols) is confined within one block. We believe that adding dependency to code bits (symbols) of different blocks of a random coding design can enhance the coding performance. In this 3-year proposal, we will investigate the rich field of random coding with interblock memory.

In the first project year, the performance of binary turbo coding with interblock memory was investigated. In this year, we study turbo coded modulation with interblock memory. In the third year, we will design turbo BLAST with interblock memory, where turbo BLAST is a randomly coded MIMO system.

### 三、研究方法(Methods)

In the first project year, we investigate the performance of binary turbo coding with interblock memory for which the encoding is implemented by serially concatenating a multiplexer, a multilevel delay processor, and a

binary signal mapper to a conventional turbo encoder. The scheme of binary turbo coding with interblock memory can also be used to construct coded modulation if the binary signal mapper is replaced by the signal mapper for a modulation constellation.

### A. Encoding

Fig. 1 shows the encoding structure of turbo coded modulation with interblock memory, T, where C is the conventional binary turbo code [1]. The output of C is split into multiple streams, and then each stream undergoes a different delay. These streams are linearly combined to form T. The code C is constructed from a rate-1/3 binary turbo code which consists of a K-bit interleaver and rate-1/2 constituent codes RSC1 and RSC2. An arbitrary code rate R > 1/3 for C can be obtained by uniformly puncturing the parity bits of RSC1 and RSC2.

Denote the *t*-th code word of a rate-1/3 turbo code word as  $\left[\overline{u}(t), \overline{p}_1(t), \overline{p}_2(t)\right]$ , where  $\overline{u}(t)$  is the message part and  $\overline{p}_1(t)$  and  $\overline{p}_2(t)$  are parity parts from RSC1 and RSC2, respectively.

Let  $\overline{u}(t) = [u(t,0), u(t,1), \cdots, u(t,K-1)]$  and  $\overline{p}_j(t) = [p_j(t,0), p_j(t,1), \cdots, p_j(t,K-1)]$ , where u(t,k) and  $p_j(t,k)$ , j=1,2,  $k=0,1,\ldots,K-1$ , are binary bits. A code word at time t,  $\overline{a}(t)$ , of rate-2/3 binary turbo code C,  $\overline{a}(t) = [\overline{u}(t), \overline{p}(t)]$ , where  $\overline{p}(t) = [p_1(t,0), p_2(t,1), p_1(t,4), p_2(t,5), \cdots, p_1(t,K-2), p_2(t,K-1)]$ , can be obtained by uniformly puncturing one fourth of parity bits of both  $\overline{p}_1(t)$  and  $\overline{p}_2(t)$ .

coded sequence The turbo  $\vec{a} = \{\cdots, \overline{a}(t), \overline{a}(t+1), \cdots\}$ is sequentially processed by the multiplexer and the delay processor to produce the associated output  $\vec{v} = \{\cdots, \overline{v}(t), \overline{v}(t+1), \cdots\}$ sequences  $\vec{s} = \{\cdots, \vec{s}(t), \vec{s}(t+1), \cdots\}$ respectively, where  $\overline{v}(t) = [\hat{v}(t,0), \hat{v}(t,1), \dots, \hat{v}(t,\lambda-1)]$  $\overline{s}(t) = [\hat{s}(t,0), \hat{s}(t,1), \dots, \hat{s}(t,\lambda-1)],$  and each of  $\hat{v}(t,k) = [v_1(t,k), \dots, v_m(t,k)]$  $\hat{s}(t,k) = [s_1(t,k), \dots, s_m(t,k)]$  is a binary *m*-tuple. Note that  $m\lambda = K/R$ . The sequence  $\vec{s}$  is then processed by a memoryless signal mapper

to produce the output sequence  $\vec{z} = \{\cdots, \bar{z}(t), \bar{z}(t+1), \cdots\}$ , where  $\bar{z}(t) = [\hat{z}(t,0), \hat{z}(t,1), \cdots, \hat{z}(t,\lambda-1)]$  and  $\hat{z}(t,k) = \omega(\hat{s}(t,k)) \in \Omega$ .  $\Omega$  is a signal constellation consisting of  $2^m$  signal points. The resultant code T takes  $\vec{z}$  as its code sequence.

For concise presentation, the indexes t and k are omitted in the remainder of this paragraph. For a constellation with 2<sup>m</sup> points, we consider q-level partition,  $q \le m$  $0 = i_0 < i_1 < \dots < i_{q-1} < i_q = m$ , where  $i_j$  is an integer. Write  $\hat{s} = [\theta_1, \dots, \theta_a]$ , where  $\theta_j = [s_{i_{j-1}+1}, s_{i_{j-1}+2}, \dots, s_{i_j}]$ . With this, we can q-level partition  $\Omega = \Omega_0 / \Omega_1 / \Omega_2 / \cdots / \Omega_q$  , where  $\Omega_{j-1}$  is partitioned into  $2^{i_j-i_{j-1}}$  cosets of  $\Omega_i$  and  $\theta_i$ represents one of the  $2^{i_j-i_{j-1}}$  cosets [9-10]. Since  $\Omega$  is a signal constellation, the distance measure  $\Delta(\hat{z}, \hat{z}')$  is the squared Euclidean distance between  $\hat{z}$  and  $\hat{z}'$ . Let  $\omega(\hat{s})$  and  $\omega(\hat{s}')$  denote two signal points which are in the same coset of  $\Omega_{i-1}$ , but in distinct cosets of  $\Omega_i$  labelled by  $\theta_i = \alpha$  and  $\theta_i = \beta$ , respectively. We define  $\Delta_i(\alpha, \beta)$  to be the least one of all the possible  $\Delta(\omega(\hat{s}), \omega(\hat{s}'))$ , and  $n_i(\alpha, \beta)$  to be the average number of signal points  $\omega(\hat{s}')$ satisfying  $\Delta(\omega(\hat{s}),\omega(\hat{s}')) = \Delta_i(\alpha,\beta)$ .

Furthermore, let  $\omega(\hat{s}), \omega(\hat{s}') \in \Omega_{j-1}$  and  $s_{i_{j-1}+k} \neq s'_{i_{j-1}+k}$ . We define  $\delta_j^{i_{j-1}+k}$ ,  $k=1,\cdots,i_j-i_{j-1}$ , to be the least one of all the possible  $\Delta(\omega(\hat{s}),\omega(\hat{s}'))$ , and  $\eta_j^{i_{j-1}+k}$  to be the average number of signal points  $\omega(\hat{s}')$  satisfying  $\Delta(\omega(\hat{s}),\omega(\hat{s}'))=\delta_j^{i_{j-1}+k}$ . Note that if q=m, then  $\delta_j^j=\Delta_j(1,0)=\Delta_j$  and  $\eta_j^j=n_j(1,0)=n_j$  for  $j=1,\cdots,m$ . The necessity of introducing the m-level parameters, i.e.,  $\eta_i^j$  and  $\delta_i^j$  for all possible i and j, in addition to the q-level parameters  $\{\Delta_1(\cdot,\cdot),\cdots,\Delta_a(\cdot,\cdot)\}$  and  $\{n_1(\cdot,\cdot),\cdots,n_a(\cdot,\cdot)\}$  is

that even though we use a q-level partition structure in the encoding, the bit-by-bit decoding used in the turbo decoding views the coding as an m-level structure.

**Example 1 :** Let m=3, q=3 and  $\{i_1,i_2,i_3\}=\{1,2,3\}$ . Consider an 8PSK signal constellation Ω with Ungerboeck's labelling [9]. It can be checked that  $\{\Delta_1(1,0)=0.586, \Delta_2(1,0)=2,\Delta_3(1,0)=4\}$ ,  $\{n_1(1,0)=2,n_2(1,0)=2,n_3(1,0)=1\}$ ,  $\{\delta_1^1=0.586,\delta_2^2=2,\delta_3^3=4\}$  and  $\{\eta_1^1=2,\eta_2^2=2,\eta_3^3=1\}$ .

**Example 2:** Let m=3, q=2 and  $\{i_1,i_2\}=\{1,3\}$ , Consider an 8PSK signal constellation  $\Omega$  with mixed labelling [6]. It can be checked that  $\{\Delta_1(1,0)=0.586, \Delta_2(00,10)=2,\Delta_2(00,01)=2,\Delta_2(00,11)=4\}$ ,  $\{n_1(1,0)=2,n_2(00,10)=1,n_2(00,01)=1,n_2(00,11)=1\}$ ,  $\{\delta_1^1=0.586,\delta_2^2=2,\delta_2^3=2\}$  and  $\{\eta_1^1=2,\eta_2^2=1,\eta_2^3=1\}$ .

With such a q-level partition, we can use a general q-level delay processor instead of the m-level delay processor to construct coded modulation. Write  $\hat{v}(t,k) = [\gamma_1(t,k),\cdots,\gamma_q(t,k)]$ , where  $\gamma_j(t,k) = [v_{i_{j-1}+1}(t,k),v_{i_{j-1}+2}(t,k),\cdots,v_{i_j}(t,k)]$ . The relationship between  $\gamma_j(t,k)$  and  $\theta_j(t,k)$  is  $\theta_j(t,k) = \gamma_j(t-(q-j),k)$  for  $1 \le j \le q$ ,  $k = 0,1,2,\cdots,\lambda-1$  and  $m\lambda = K/R$ .

We can use either IDSC or IDAC to decode T in the case of coded modulation. Note that, for either IDSC or IDAC, the extrinsic value for each labelling bit is calculated in bit level rather than in symbol level in the MAP demapper since the bit-by-bit decoding is used in the turbo decoding of *C*.

### **B.** Two specific constructions

We now consider the design of TCM with rate of 2 bits per 8PSK symbol. Let C be a rate-2/3 conventional binary turbo code with an interleaver size of K message bits. Let  $\overline{a}(t) = [\overline{u}(t), \overline{p}(t)]$  be the t-th codeword of C, where  $\overline{p}(t) = [p_1(t,0), p_2(t,1), p_1(t,4), p_2(t,5), \cdots, p_1(t,K-2), p_2(t,K-1)]$ .

Construction A: We use the parameters of m,

$\Omega$ , q,  $\{i_i, i_2\}$  and the signal labelling as given in Example 2. The relation between inputs and outputs of the multiplexer is described by  $v_1(t,k) = u(t,2k)$  and  $v_2(t,k) = u(t,2k+1)$ . In addition,  $v_3(t,k) = p_1(t,2k)$  for even k and  $v_3(t,k) = p_2(t,2k-1)$  for odd k. Let  $\lambda = K/2$ . The relation between inputs and outputs of the delay processor described is by  $s_1(t,k) = v_1(t-1,k)$  ,  $s_2(t,k) = v_2(t,k)$ and  $s_3(t,k) = v_3(t,k)$  ,  $k = 0,1,\dots, \lambda - 1$  . The relation among  $\vec{s}$ ,  $\vec{v}$  and  $\vec{a}$  is given in Fig. 2. The resultant code T is a TCM with rate 2 bits per 8PSK symbol.

We may consider a modified version of Construction A which denoted is Construction A' by employing Ungerboeck's labelling instead of mixed labelling and a three-level delay processor, i.e., m = q = 3 and  $\lambda = K/2$  which yields  $\{\Delta_1(1,0) = 0.586,$  $\Delta_2(1,0) = 2, \Delta_3(1,0) = 4$  and  $\{\eta_1^1 = 2, \eta_2^2 = 2, \eta_3^3\}$ = 1}. Although the asymptotic performance is quite good,  $\{\eta_1^1 = 2, \eta_2^2 = 2, \eta_3^3 = 1\}$  implies a dense distance spectrum and hence causes poor error performance by using IDSC for the SNR of interested to us. In addition, the decoding delay will be increased. Although we can use IDAC to decode Construction A' for reducing the increased error coefficients, we must respectively apply IDSC to  $\overline{a}(t)$ ,  $\overline{a}(t+1)$ , and  $\overline{a}(t+2)$  to sufficiently reduce the increased error coefficients and hence the decoding complexity is significantly increased. Moreover, the decoding delay is further increased.

Suppose that we switch the positions of u(t,2k) and  $p_1(t,2k)$ , and switch the positions of u(t,2(k+1)) and  $p_2(t,2k+1)$ , where k is an even integer. Then, the message for which u(t,2k) and u(t,2(k+1)) are zero for all the even k will greatly reduce the code distance. A compromise given in the following construction can obtain less code distance but thinner distance spectrum as compared to Construction A.

**Construction B:** This construction is the same as Construction A except that we switch the

positions of u(t,2(k+1)) and  $p_2(t,2k+1)$ , where k is an even integer.

In T, the code bits of C are split into the streams with different delays before being fed into the signal mapper. This design allows streams with different delays to have different levels of protection. Hence, T provides some kind of irregularity for the code bits of C. Furthermore, we can provide a variety of irregularity by considering the construction Tc which employs various degrees of interblock memory. Tc is obtained by passing only a fraction,  $P_{IB}$ , of the code bits of C through the delay processor, while the input of the signal mapper is the combination of the output of the delay processor and the remaining bits of C. By varying the fraction,  $P_{IB}$ , we can have  $T_C$ with various irregularity and error performance.

consider coded modulation we can various degrees constructed from of combination of Construction A (or Construction B) and the TTCM in [3]. The TTCM in [3] is constructed by appending to the encoder of a binary turbo code C a multiplexer, an interleaver, and a signal mapper. The labelling used in the signal mapper of the TTCM in [3] is the Gray labelling. For Construction A or B with  $P_{IB}=1$ , the decoding delay is 2K message bits, i.e., K 8PSK symbols, if IDSC is used. If IDAC is used, the decoding delay becomes 3K message bits. In general, for Construction A or B with  $P_{IB} = \varepsilon$ , the decoding delay is  $2K\varepsilon + (1-\varepsilon)K$ message bits if IDSC is used. If IDAC is used, the decoding delay becomes  $3K\varepsilon + (1-\varepsilon)2K$ message bits. For the TTCM in [3], the decoding delay is K message bits.

#### C. Distance properties

With the general q-level delay processor and the signal mapper, we can check the distance properties of the resultant code T in a manner similar to that used in [8]. Let  $\vec{v} = \{\cdots, \vec{v}(-1), \vec{v}(0), \cdots\}$  be a weight-d binary sequence that is the multiplexed version of a turbo coded sequence  $\vec{a}$  from C. Let  $\vec{z}$  and  $\vec{z}_0$  be the output sequences associated with  $\vec{v}$  and  $\vec{0}$ , respectively, where  $\vec{0}$  is the all zero

sequence. Assume  $\overline{v}(t) = \overline{0}$  for t < 0 and  $\overline{v}(0) \neq \overline{0}$ , where  $\overline{0}$  is the all zero codeword consisting of  $\lambda$  binary m-tuples. The pairwise distance measure  $\Delta(\vec{z}, \vec{z}_0)$  between sequences  $\vec{z}$  and  $\vec{z}_0$  is lower bounded by  $\Delta_{LB}(\vec{v}, \vec{0}) = \sum_{j=1}^q \sum_{k=0}^{\lambda-1} \Delta_j(\gamma_j(0,k), \hat{0}_j)$ , where  $\hat{0}_j$  denotes the all zero  $(i_j - i_{j-1})$ -tuple.

# D. Iterative decoding within a single codeword (IDSC)

We illustrate IDSC for Construction A. Extension other constructions straightforward. Fig. 2 shows the relation among sequences  $\vec{s}$ ,  $\vec{v}$ and Construction A, where  $\vec{a}$ ,  $\vec{v}$  and  $\vec{s}$  are the output sequences of the encoder of C, the multiplexer, and the delay processor, respectively. Let  $\bar{z}(t)$  be the transmitted word and  $\overline{y}(t)$  be the received word. For j=1,2,3, write

$$\overline{v}_{i}(t) = [v_{i}(t,0), v_{i}(t,1), \dots, v_{i}(t,\lambda-1)].$$

Now consider the decoding of  $\overline{a}(t)$ . The decoder of IDSC consists of a MAP (maximum a posteriori probability) demapper and a turbo decoder of C. Suppose the extrinsic L-values (or log-likelihood ratios)  $L_{D,e}(\overline{a}(t-1)) = L_{D,p}(\overline{a}(t-1)) - L_{D,c}(\overline{a}(t-1))$  of bits in  $\overline{a}(t-1)$  have been obtained from the decoding of  $\overline{a}(t-1)$ , where  $L_{D,p}(\overline{a}(t-1))$  and  $L_{D,c}(\overline{a}(t-1))$  are the associated *a posteriori* and channel values.

Step 1 The demapper computes the posteriori L-values  $L_{M,p}(\overline{v}_2(t))$  of bits in  $\overline{v}_2(t)$  and  $L_{M,p}(\overline{v}_3(t))$  of bits in  $\overline{v}_3(t)$ , based on the received word  $\overline{v}(t)$ and the priori L-values a  $L_{M,a}(\overline{v}_1(t-1)) = 0$ which can obtained from  $L_{D,e}(\overline{a}(t-1))$ . Similarly, the demapper computes  $L_{M,p}(\overline{v}_1(t))$ based  $\overline{y}(t+1)$ on  $L_{M,a}(\overline{v}_2(t+1)) = L_{M,a}(\overline{v}_3(t+1)) = 0$ . In

the calculation of  $L_{M,p}(\overline{v}(t))$ , the values  $L_{M,a}(\overline{v}(t))$  are zero and hence the values  $L_{M,p}(\overline{v}(t))$  equal the extrinsic values  $L_{M,e}(\overline{v}(t))$ .

Step 2 The turbo decoder of Cuses  $L_{M,p}(\overline{v}(t))$ as channel value  $L_{D,c}(\overline{a}(t))$  for bits in  $\overline{a}(t)$  to recover bits of  $\overline{a}(t)$ and obtain values  $L_{D,e}(\overline{a}(t))$  which are stored for the calculation of  $L_{M,n}(\overline{v}_2(t+1))$  and  $L_{M,p}(\overline{v}_3(t+1))$ .

Throughout this paper, the Max-Log-MAP algorithm with correction factors [11-12] is employed and  $N_I$  denotes the number of iterations for the decoding of C.

In C, this weight-d binary sequence,  $\vec{v}$ , contributes to only "one" neighbor in counting N(d), where N(d) is the multiplicity of codewords of weight d. For T with IDSC, this weight-d binary sequence,  $\vec{v}$ , may contribute more than one in counting  $N(\Delta_{LB}(\vec{v},\vec{0}))$ . Specifically, the code sequence,  $\vec{v}$ , contributes to

$n(\vec{v}, \vec{0}) = \prod_{j=1}^{q} \prod_{k=1}^{i_j - i_{j-1}} \prod_{\ell=1}^{\lambda - 1} [\eta_j^{i_{j-1} + k}]^{v_{i_{j-1} + k(0,\ell)}}$ (1)

neighbors in counting  $N(\Delta_{LB}(\vec{v}, \vec{0}))$ .

# E. Iterative decoding between adjacent codewords (IDAC)

For T, IDSC results in large error coefficients as indicated in equation (1). The error coefficients can be reduced and hence the performance can be improved by iteratively decoding between two adjacent turbo code words,  $\overline{a}(t)$  and  $\overline{a}(t+1)$ . This decoding is referred to as iterative decoding between adjacent codewords (IDAC). We illustrate the for Construction decoding of  $\overline{a}(t)$ Extension other constructions is to straightforward. Suppose that  $L_{D,e}(\overline{a}(t-1))$ has been obtained.

**Step 1** Based on  $L_{D,e}(\overline{a}(t)) = 0$  (equivalently  $L_{M,a}(\overline{v}(t)) = 0$  ), we use IDSC to

decode  $\overline{a}(t+1)$  and obtain  $L_{D,e}(\overline{a}(t+1))$ . In the demapper, the calculation of  $L_{M,p}(\overline{v}(t+1))$  is based on  $L_{M,q}(\overline{v}(t)) = 0$ .

**Step 2**Based on  $L_{D,e}(\overline{a}(t+1))$  obtained in Step 1,  $L_{D,e}(\overline{a}(t-1))$  and  $L_{M,a}(\overline{v}(t)) = 0$ , the demapper calculates  $L_{M,p}(\overline{v}(t))$ . The decoder of C then use  $L_{M,p}(\overline{v}(t))$  as  $L_{D,c}(\overline{a}(t))$  to decode  $\overline{a}(t)$  and obtain  $L_{D,e}(\overline{a}(t))$ .

**Step 3** Based on  $L_{D,e}(\overline{a}(t))$  obtained in Step 2, we use IDSC to re-decode  $\overline{a}(t+1)$  and update  $L_{D,e}(\overline{a}(t+1))$ .

**Step 4** Based on updated  $L_{D,e}(\overline{a}(t+1))$  obtained in Step 3,  $L_{D,e}(\overline{a}(t-1))$ , and  $L_{M,a}(\overline{v}(t)) = 0$ , the demapper calculates of  $L_{M,p}(\overline{v}(t))$ . The decoder of C uses updated  $L_{M,p}(\overline{v}(t))$  as new channel values  $L_{D,e}(\overline{a}(t))$  to decode  $\overline{a}(t)$  and obtain  $L_{D,e}(\overline{a}(t))$ .

**Step 5** After repeating Steps 3 and 4 for  $N_{IDAC}$  –1 times, we can recover  $\overline{a}(t)$  and obtain  $L_{D.e.}(\overline{a}(t))$ .

In the above,  $N_I$  iterations are used for each turbo decoding of C.

#### 四、研究成果(Results)

We now consider the error performance of Constructions A and B. In the following, BER simulation and analysis of EXIT charts in AWGN channels are given. The constituent codes used in these examples are 4-state and 16-state codes with generator matrices given by  $(1,5/7)_8$  and  $(1,37/21)_8$ , respectively.

# A. BER results for short-to-moderate code lengths

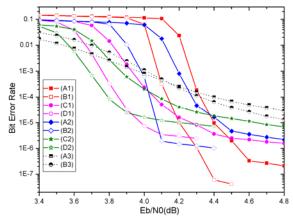

The simulation of 4-state Constructions A and B with  $P_{IB} = 1$  (or  $P_{IB} = 4/8$ ) and K = 2048 by using either IDSC or IDAC is performed. The simulation of 4-state TTCM constructed

from [3] is also performed for comparison. The simulation results are given in Fig. 3. From Fig. 3, we can see that the error performance of Construction A or B is better than that of TTCM [3] at moderate-to-high SNR not only for the same interleaver size but also for the same decoding delay. In particular, the 4-state Construction A with K = 2048,  $P_{IB} = 4/8$  can achieve a BER of 10<sup>-5</sup> at an Eb/No of 4.3 dB and 4.0 dB, respectively if IDSC and IDAC are respectively used, while for the 4-state TTCM [3] with K = 4096, the associated BER is around  $2 \times 10^{-5}$  at  $E_b/N_o=4.7$  dB. The 4-state Construction A with K = 2048,  $P_{IB} = 4/8$  can achieve a BER of  $10^{-4}$  at an  $E_b/N_o$  of 4.05 dB and 3.85dB respectively if IDSC and IDAC are respectively used, while for the 4-state TTCM [3] with K = 4096, to achieve BER =  $10^{-4}$ ,  $E_b/N_o=4.3$  dB is needed.

We also observe that the error performance at high SNR of Construction A or B can be improved by increasing *Pib*. Construction A or B can achieve much better error performance with higher decoding complexity by using IDAC as compared to using IDSC. In addition, Construction A is suitable for low BER (or high SNR) conditions while Construction B is suitable for moderate BER (or moderate SNR) conditions.

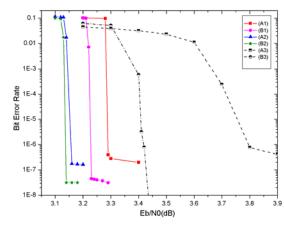

### B. BER results for long code lengths

We **BER** perform simulation for Construction B with large K to see whether the proposed TTCM can achieve the near-capacity performance. The simulation results are given in Fig. 4. We also perform the analysis of EXIT charts [7] to obtain the pinch-off SNR limits. The results of BER in the error floor region and pinch-off limits are also given in Table I. Also included in Table I are the simulation results of the TTCM constructed from [3]. We see that, Construction B with K =262144 can achieve a BER of  $3.18\times10^{-8}$  at  $E_b/N_o = 3.14$  dB which is slightly better than the threshold (pinch-off SNR) of 3.15 dB for the irregular LDPC-CM given in [5]. In addition, the pinch-off limits of 4-state and 16-state Construction B using IDAC are 3.10 dB and 3.05 dB, which are only 0.20 and 0.15 from the constraint capacity dΒ

dB),respectively.

### 五、結論與討論(Concluding Remarks)

In this research, the performance of turbo coded modulation with interblock memory is investigated. Coded modulation,  $T_C$ , can be constructed based on various degrees of interblock memory and decoded by using either IDSC or IDAC. Simulation shows that for short-to-long code lengths, the error performance of turbo coded modulation with interblock memory, in general, is better than that of the conventional TTCM[3], moderate-to-high SNR. The simulation results are confirmed by the analysis of EXIT charts. We expect that there is advantage in introducing interblock memory to other random-like codes such as (irregular) LDPC codes, (irregular) RA codes, random coded MIMO, etc...

### 六、參考文獻(References)

- [1] C. Berrou, A. Glavieux, and P. Thitimajshima, "Near Shannon limit error-correcting coding and decoding: turbo-codes(1)," in *Proc. IEEE ICC* (Geneva, Switzerland, May 1993) pp. 1064-1070.

- [2] T.J. Richardson, M.A. Shokrollahi, and R.L. Urbanke, "Design of Capacity-Approaching Irregular Low-Density Parity-Check Codes," *IEEE Trans. Inform. Theory*, vol. 47, no. 2, pp. 619-637, Feb. 2001.

- [3] S. Le Goff, A. Glavieux and C. Berrou, "Turbo-codes and high spectral efficient modulation," in Proc. ICC'94, pp. 1064-1070, 1994.

- [4] G. Caire, G. Taricco, and E. Biglieri, "Bit-interleaved coded modulation," *IEEE Trans. Inform.*, vol. 44, pp. 927-946, May 1998.

- [5] D. Sridhara, and T. E. Fuja, "LDPC codes over rings for PSK modulation," *IEEE Trans. Inform. Theory*, vol. 51, no. 9,pp. 3209–3220, Sept. 2005.

- [6] X. Li and A. Ritcey, "Bit-Interleaved coded modulation with iterative decoding," IEEE Commun. Letters, vol. 1, no. 6, pp. 77–79, Nov. 1997.

- [7] S. ten Brink, "Convergence behavior of iteratively decoded parallel concatenated codes," *IEEE Trans. Commun.*, vol. 49, no. 10, pp. 1727-1737, Oct 2001.

- [8] J.Y. Wang and M.C. Lin, "On constructing trellis codes with large free distances and low decoding complexities," *IEEE Trans. on Commun.*, vol.45, No.9, pp.1017-1020, Sept. 1997.

- [9] G. Ungerboeck, "Channel coding with multilevel/phase signals," IEEE Trans. Inform.

Theory, vol.IT-28, no.1, pp.55-67, Jan. 1982.

- [10] G. Pottie and D. Taylor, "Multilevel codes based on partitioning," *IEEE Trans. Inform. Theory*, vol.35, pp.87-98, Jan. 1989.

- [11] J. Hagenauer, E. Offer, and L. Papke, "Iterative decoding of binary block and convolutional codes," *IEEE Trans. Inform. Theory*, vol.42, no.2, pp.429-445, Mar. 1996.

- [12] P. Robertson, E. Villebrun, and P. Hoeher,"A comparison of optimal and suboptimal MAP decoding algorithms operating in the log domain," in Proc. ICC '95, pp.1009-1013.

### 六、圖表 (Figures and Tables)

Fig. 1: Encoding structure of binary turbo coding with interblock memory

|       | $\hat{s}(t,0)$               | $\hat{s}(t,1)$               | • • • | $\hat{s}(t+1,0)$               | $\hat{s}(t+1,1)$                 | • • • | $\hat{s}(t+2,0)$                     | $\hat{s}(t+2,1)$                     |

|-------|------------------------------|------------------------------|-------|--------------------------------|----------------------------------|-------|--------------------------------------|--------------------------------------|

| $s_1$ | $u(t-1,0)$ = $v_1(t-1,0)$    | u(t-1,2)<br>= $v_1(t-1,1)$   |       | u(t, 0)<br>= $v_1(t, 0)$       | $u(t, 2)$ = $v_1(t, 1)$          |       | u(t+1,0)<br>= $v_1(t+1,0)$           | u(t + 1, 2)<br>= $v_1(t + 1, 1)$     |

| $s_2$ | $u(t, 1)$ = $v_2(t, 0)$      | u(t, 3)<br>=<br>$v_2(t, 1)$  |       | u(t+1,1)<br>= $v_2(t+1,0)$     | u(t+1,3)<br>= $v_2(t+1,1)$       |       | u(t + 2, 1)<br>= $v_2(t + 2, 0)$     | u(t + 2, 3)<br>=<br>$v_2(t + 2, 1)$  |

| $s_3$ | $p_1(t, 0)$<br>= $v_3(t, 0)$ | $p_2(t, 1)$<br>= $v_3(t, 1)$ |       | $p_1(t+1,0)$<br>= $v_3(t+1,0)$ | $p_2(t+1, 1)$<br>= $v_3(t+1, 1)$ | • • • | $p_1(t + 2, 0)$<br>= $v_3(t + 2, 0)$ | $p_2(t + 2, 1)$<br>= $v_3(t + 2, 1)$ |

Fig.2: Relation among sequences  $\vec{s}$  ,  $\vec{v}$  and  $\vec{a}$  for Construction A

Fig.3: Simulation for 4-state Construction A (Constr. A), Construction B (Constr. B), and TTCM [3] with  $N_I\!=\!10$ .

- (A1) Constr. A, IDSC, P<sub>IB</sub>=1, K=2048.

- (B1) Constr. A, IDAC, P<sub>IB</sub>=1, N<sub>IDAC</sub>=3, K=2048.

- (C1) Constr. A, IDSC, P<sub>IB</sub>=4/8, K=2048.

- (D1) Constr. A, IDAC, P<sub>IB</sub>=4/8, N<sub>IDAC</sub> =3, K=2048.

- (A2) Constr. B, IDSC, P<sub>IB</sub>=1, K=2048.

- (B2) Constr. B, IDAC, P<sub>IB</sub>=1, N<sub>IDAC</sub>=3, K=2048.

- (C2) Constr. B, IDSC, P<sub>IB</sub>=4/8, K=2048.

- (D2) Constr. B, IDAC, P<sub>IB</sub>=4/8, N<sub>IDAC</sub>=3, K=2048.

- (A3) 4-state TTCM[3], K=2048.

- (B3) 4-state TTCM[3], K=4096.

Fig.4: Simulation for Construction B (Constr. B) with  $P_{IB}$ =8/8 and TTCM[3]. All results are based on  $N_I$ =18.

- (A1) 4-state Constr. B, IDSC, K=262144.

- (B1) 4-state Constr. B, IDAC, N<sub>IDAC</sub> = 3, K=262144

- (A2)16-state Constr. B, IDSC, K=262144.

- (B2)16-state Constr. B, IDAC, NIDAC = 3, K=262144

- (A3):4-state TTCM[3], K=262144.

- (B3):4-state TTCM[3], K=524288.

#### TABLE I

Results of pinch-off limits and BER in the error-floor regions for construction B and TTCM [3]. The BER simulation is based on  $N_I$ =18, and K=262144 and K=524288 for construction B and TTCM[3], Respectively.

|      | Con                               | struction B (4 | -state)               | Construction B (16-state) |                         |                       |  |

|------|-----------------------------------|----------------|-----------------------|---------------------------|-------------------------|-----------------------|--|

|      | Pinch-off                         | Error Floor    | Performance           | Pinch-off                 | Error Floor Performance |                       |  |

|      | Limits(dB)                        | Eb/No(dB)      | BER                   | Limits(dB)                | Eb/No(dB)               | BER                   |  |

| IDSC | 3.27                              | 3.30           | $2.81 \times 10^{-7}$ | 3.12                      | 3.16                    | $1.77 \times 10^{-7}$ |  |

| IDAC | 3.10                              | 3.23           | $4.53 \times 10^{-8}$ | 3.05                      | 3.14                    | $3.18 \times 10^{-8}$ |  |

|      | Т                                 | TCM[3] (4-sta  | ate)                  | TTCM[3] (16-state)        |                         |                       |  |

|      | Pinch-off Error Floor Performance |                |                       | Pinch-off                 | Error Floor Performance |                       |  |

|      | Limits(dB)                        | Eb/No(dB)      | BER                   | Limits(dB)                | Eb/No(dB)               | BER                   |  |

|      | 3.55                              | 3.8            | $7.72 \times 10^{-7}$ | 3.25                      | 3.40                    | $2.43 \times 10^{-6}$ |  |

### 參加 2006 International Symposium on Information Theory and Its

# Applications 心得報告 林茂昭

## 國立台灣大學電機工程學系 mclin@cc.ee.ntu.edu.tw

日本的消息理論及其應用學會(Society of Information Theory and Its Applications, SITA)成立於 1978 年。在日本國內每年舉辦一次學術會議,即 Symposium on Information Theory and Its Applications。由於在日本研究消息理論 的人員很多,因此 SITA 所舉辦的 Symposium on Information Theory and Its Applications 頗受到國際消息理論學術界重視。因此錯誤更正碼領域大師林舒教授(Professor Shu Lin)建議 SITA 可以每兩年舉辦一次國際性學術會議,稱之為 International Symposium on Information Theory and Its Applications (ISITA),即國際消息理論及其應用會議。第一次 ISITA 於 1990 年在美國夏威夷舉行,第二次 ISITA 於 1992 年在新加坡舉行,第三次 ISITA 於 1994 年在澳大利亞雪梨舉行,第四次 ISITA 於 1996 年在加拿大維多利亞(Victoria)舉行,第五次 ISITA 於 1998 年在墨西哥舉行,第六次 ISITA 於 2000 年,即十周年時又回到在美國夏威夷,第七次 ISITA 於 2002 年在中國大陸西安舉行,第八次 ISITA 於 2004 年在義大利帕爾瑪(Parma)舉行,這是頭一次 ISITA 於亞太地區之外舉行,第九次 ISITA 於今年,2006 年 10 月 29 日至 11 月 1 日在南韓首爾(漢城)之 COEX 國際會議中心舉行。

顧名思義,國際消息理論及其應用會議(ISITA)之研討重點為消息理論。全世界最重要之相關學術會議為 IEEE 國際消息理論會議(IEEE International Symposium on Information Theory, IEEE ISIT)。ISITA 為規模僅次於 IEEE ISIT 之消息理論學術會議。此外其他較有歷史之消息理論相關學術會議為普林斯頓大學與約翰霍普金斯大學所輪流舉辦之 Conference on Information Sciences and Systems (CISS),但是規模比 ISITA 小很多。在 1990 年第一次 ISITA 時曾經特別恭請錯誤更正碼大師 Forney 博士演講對錯誤更正碼領域之未來展望。過了十來年又逢 ISITA,回過頭看這些年之變化,錯誤更正碼領域的研究大幅進步,其成果似乎遠超過先前所有人之預測,除了消息理論之父 C.E. Shannon 之外。

今年之 ISITA 的兩位大會共同主席(General Co-Chairs)為日本 Chuo University 之 Hideki Imai 教授及南韓國立首爾大學 Jong-Seon No 教授。學術議程共同主席(Technical Program Co-Chairs)為日本 Osaka University 之 Toru Fujiwara

教授及南韓 Hongik University 之 Habong Chung 教授。我本人則擔任學術議程委員,負責一部分投稿論文之送審及推薦之工作。這一次 ISITA 共有來自 18 個國家的 217 篇投稿,而最後有 177 篇論文被接受而於會中發表。

去年五月我曾來過南韓首爾 COEX 國際會議中心參加 2005 年國際通訊會議 (IEEE International Conference on Communications, ICC)。對於南韓仁川國際機場至 ISITA 會議地點已經有一些瞭解,因此對於行程之安排不需費心。十月二十九日搭乘長榮航空班機於晚間抵達南韓仁川國際機場。此行一路上還算順利,但是在檢查護照的入境海關前看到一團混亂的等待人潮就想這下有得等了。果然排隊通關花了近四十分鐘。在排隊人龍之前沒有管理人員適當之導引與設法排解長龍。心中不禁納悶在科技製造研發相當先進之南韓其管理服務似乎不甚理想。入境之事務,攸關國家門面應該多費些心思才對。

十月三十日一早趕去會場聆聽大會安排之大會演說。其中第一場由 Harvard University 的 Valid Tarokh 教授講演,主題為"Collaboration, Competition and Cognitive Radio Transmission in Wireless Networks,",討論 wireless sensor networks 操作的三種模式,包括目前已經為人熟知且廣汎研究的競爭 Competition 模式和較少被提及之合作 Collaboration 模式以及認知無線傳輸 Cognitive Radio Transmission 模式。我個人覺得 Competition 模式應可涵蓋其他兩種模式。第二場由南韓 Sogang University 之 Daehyoung Hong 教授演講,主題為"WiBro: A Wireless Broadband Technology",說明南韓對 WiBro 之研發過程,於演講之中感受到南韓之努力,也加深了對自己之警惕。第三場由日本 NTT Laboratories 之 Tatsuaki Okamoto 博士演講,主題為"How to Prove the Security of Cryptography",對於此領域我已經多年未接觸,因此沒什麼感覺。

大會演講之後,展開兩天的分組學術論文發表與討論,在同一時段有五個分 組同時進行。主題有

Coding Theory, Network Security, Source Coding, Spread Spectrum Systems, MIMO, LDPC Codes, Data Security, Shannon Theory, Ultra Wide Band, Public Key Cryptography Multi-User Information, CDMA, Iterative Decoding, Data Network, Network Coding, Mobile Communications, OFDM, Weight Distribution, Quantum Information, Random Number, Sensor Networks, Image and Speech, Coded Modulation and Space-Time Codes, Pattern Recognition, Ad Hoc Networks, Sequences 等。

我個人發表的論文為"Improved Decoding for Trellis Coded Modulation with a Convolutional Processor,"內容是針對以往設計之一種具大自由距離之籬柵式編碼 調變設計改善錯誤率之解碼方式。先前之簡化解碼方式造成了大數量的錯誤係數

(近距離的路徑數目),因此在低訊雜比的狀況下解碼錯誤率並不理想。在此論文中我們以乘積式籬柵(product trellis)來進行解碼,可以降低錯誤係數,也因而得以降低錯誤率。我在會議中遇到美國夏威夷大學的 Marc Fossorrier 教授,他對於此研究很感興趣,也建議一些可以進一步改善錯誤率之方向。此外,他也提到今年一位前往美國夏威夷大學接受他指導的攻讀博士學位的學生王仲立。Fossorrier 教授覺得王仲立資質很好,基礎紮實。這位王仲立同學先前曾在我指導之下獲得台大電信所碩士學位。

我參加過多次 ISITA 並且在 2004 ISITA 及 2006 ISITA.都擔任學術議程委員,覺得這一次 ISITA 投稿數及參與會議人數都沒有以往熱烈估計。原因是近年有許多 IEEE 通訊領域的學術會議都接受消息理論領域之論文發表。這些論文可記錄於 IEEE Xplore 資料庫,方便他人於網路檢索。因此許多研究人員都樂於投稿於這些學術會議。目前發表於 ISITA 之論文則缺乏類似的資料庫支援網路檢索。我與 Fujiwara 教授談及此論點,Fujiwara 教授提及 ISITA 建立資料庫所面臨的一些問題,也會設法來解決處理。此外我來首爾之前受 IEEE Information Theory Society Taipei Chapter 的 Chapter Chair 韓永祥教授之託,來探詢在台灣舉辦 ISITA 之可能性。Fujiwara 教授告知 2008 ISITA 已經確定將於 New Zealand Auckland 舉行。因為台灣極可能舉辦 2010 IEEE VTC,所以我就沒有再探詢在台灣舉辦 2010 ISITA 之可能性。於大會進行中得知南韓又將舉辦 2009 IEEE ISIT 心中頗有一些失落感。

### 參加 2006 International Symposium on Information Theory and Its

# Applications 心得報告 林茂昭

## 國立台灣大學電機工程學系 mclin@cc.ee.ntu.edu.tw

日本的消息理論及其應用學會(Society of Information Theory and Its Applications, SITA)成立於 1978 年。在日本國內每年舉辦一次學術會議,即 Symposium on Information Theory and Its Applications。由於在日本研究消息理論 的人員很多,因此 SITA 所舉辦的 Symposium on Information Theory and Its Applications 頗受到國際消息理論學術界重視。因此錯誤更正碼領域大師林舒教授(Professor Shu Lin)建議 SITA 可以每兩年舉辦一次國際性學術會議,稱之為 International Symposium on Information Theory and Its Applications (ISITA),即國際消息理論及其應用會議。第一次 ISITA 於 1990 年在美國夏威夷舉行,第二次 ISITA 於 1992 年在新加坡舉行,第三次 ISITA 於 1994 年在澳大利亞雪梨舉行,第四次 ISITA 於 1996 年在加拿大維多利亞(Victoria)舉行,第五次 ISITA 於 1998 年在墨西哥舉行,第六次 ISITA 於 2000 年,即十周年時又回到在美國夏威夷,第七次 ISITA 於 2002 年在中國大陸西安舉行,第八次 ISITA 於 2004 年在義大利帕爾瑪(Parma)舉行,這是頭一次 ISITA 於亞太地區之外舉行,第九次 ISITA 於今年,2006 年 10 月 29 日至 11 月 1 日在南韓首爾(漢城)之 COEX 國際會議中心舉行。

顧名思義,國際消息理論及其應用會議(ISITA)之研討重點為消息理論。全世界最重要之相關學術會議為 IEEE 國際消息理論會議(IEEE International Symposium on Information Theory, IEEE ISIT)。ISITA 為規模僅次於 IEEE ISIT 之消息理論學術會議。此外其他較有歷史之消息理論相關學術會議為普林斯頓大學與約翰霍普金斯大學所輪流舉辦之 Conference on Information Sciences and Systems (CISS),但是規模比 ISITA 小很多。在 1990 年第一次 ISITA 時曾經特別恭請錯誤更正碼大師 Forney 博士演講對錯誤更正碼領域之未來展望。過了十來年又逢 ISITA,回過頭看這些年之變化,錯誤更正碼領域的研究大幅進步,其成果似乎遠超過先前所有人之預測,除了消息理論之父 C.E. Shannon 之外。

今年之 ISITA 的兩位大會共同主席(General Co-Chairs)為日本 Chuo University 之 Hideki Imai 教授及南韓國立首爾大學 Jong-Seon No 教授。學術議程共同主席(Technical Program Co-Chairs)為日本 Osaka University 之 Toru Fujiwara

教授及南韓 Hongik University 之 Habong Chung 教授。我本人則擔任學術議程委員,負責一部分投稿論文之送審及推薦之工作。這一次 ISITA 共有來自 18 個國家的 217 篇投稿,而最後有 177 篇論文被接受而於會中發表。

去年五月我曾來過南韓首爾 COEX 國際會議中心參加 2005 年國際通訊會議 (IEEE International Conference on Communications, ICC)。對於南韓仁川國際機場至 ISITA 會議地點已經有一些瞭解,因此對於行程之安排不需費心。十月二十九日搭乘長榮航空班機於晚間抵達南韓仁川國際機場。此行一路上還算順利,但是在檢查護照的入境海關前看到一團混亂的等待人潮就想這下有得等了。果然排隊通關花了近四十分鐘。在排隊人龍之前沒有管理人員適當之導引與設法排解長龍。心中不禁納悶在科技製造研發相當先進之南韓其管理服務似乎不甚理想。入境之事務,攸關國家門面應該多費些心思才對。

十月三十日一早趕去會場聆聽大會安排之大會演說。其中第一場由 Harvard University 的 Valid Tarokh 教授講演,主題為"Collaboration, Competition and Cognitive Radio Transmission in Wireless Networks,",討論 wireless sensor networks 操作的三種模式,包括目前已經為人熟知且廣汎研究的競爭 Competition 模式和較少被提及之合作 Collaboration 模式以及認知無線傳輸 Cognitive Radio Transmission 模式。我個人覺得 Competition 模式應可涵蓋其他兩種模式。第二場由南韓 Sogang University 之 Daehyoung Hong 教授演講,主題為"WiBro: A Wireless Broadband Technology",說明南韓對 WiBro 之研發過程,於演講之中感受到南韓之努力,也加深了對自己之警惕。第三場由日本 NTT Laboratories 之 Tatsuaki Okamoto 博士演講,主題為"How to Prove the Security of Cryptography",對於此領域我已經多年未接觸,因此沒什麼感覺。

大會演講之後,展開兩天的分組學術論文發表與討論,在同一時段有五個分 組同時進行。主題有

Coding Theory, Network Security, Source Coding, Spread Spectrum Systems, MIMO, LDPC Codes, Data Security, Shannon Theory, Ultra Wide Band, Public Key Cryptography Multi-User Information, CDMA, Iterative Decoding, Data Network, Network Coding, Mobile Communications, OFDM, Weight Distribution, Quantum Information, Random Number, Sensor Networks, Image and Speech, Coded Modulation and Space-Time Codes, Pattern Recognition, Ad Hoc Networks, Sequences 等。

我個人發表的論文為"Improved Decoding for Trellis Coded Modulation with a Convolutional Processor,"內容是針對以往設計之一種具大自由距離之籬柵式編碼 調變設計改善錯誤率之解碼方式。先前之簡化解碼方式造成了大數量的錯誤係數

(近距離的路徑數目),因此在低訊雜比的狀況下解碼錯誤率並不理想。在此論文中我們以乘積式籬柵(product trellis)來進行解碼,可以降低錯誤係數,也因而得以降低錯誤率。我在會議中遇到美國夏威夷大學的 Marc Fossorrier 教授,他對於此研究很感興趣,也建議一些可以進一步改善錯誤率之方向。此外,他也提到今年一位前往美國夏威夷大學接受他指導的攻讀博士學位的學生王仲立。Fossorrier 教授覺得王仲立資質很好,基礎紮實。這位王仲立同學先前曾在我指導之下獲得台大電信所碩士學位。

我參加過多次 ISITA 並且在 2004 ISITA 及 2006 ISITA.都擔任學術議程委員,覺得這一次 ISITA 投稿數及參與會議人數都沒有以往熱烈估計。原因是近年有許多 IEEE 通訊領域的學術會議都接受消息理論領域之論文發表。這些論文可記錄於 IEEE Xplore 資料庫,方便他人於網路檢索。因此許多研究人員都樂於投稿於這些學術會議。目前發表於 ISITA 之論文則缺乏類似的資料庫支援網路檢索。我與 Fujiwara 教授談及此論點,Fujiwara 教授提及 ISITA 建立資料庫所面臨的一些問題,也會設法來解決處理。此外我來首爾之前受 IEEE Information Theory Society Taipei Chapter 的 Chapter Chair 韓永祥教授之託,來探詢在台灣舉辦 ISITA 之可能性。Fujiwara 教授告知 2008 ISITA 已經確定將於 New Zealand Auckland 舉行。因為台灣極可能舉辦 2010 IEEE VTC,所以我就沒有再探詢在台灣舉辦 2010 ISITA 之可能性。於大會進行中得知南韓又將舉辦 2009 IEEE ISIT 心中頗有一些失落感。