# High-Power High-Speed Ga<sub>0.51</sub>In<sub>0.49</sub>P/In<sub>x</sub>Ga<sub>1-x</sub>As Doped-Channel FET's

Yo-Sheng Lin and Shey-Shi Lu

Department of Electrical Engineering National Taiwan University, Taipei, Taiwan, ROC.

#### Introduction

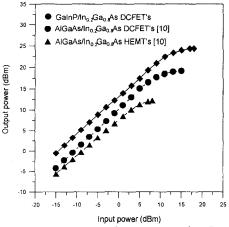

The first  $Ga_{0.51}In_{0.49}P/In_xGa_{1-x}As$  ( $0 \le x \le 0.22$ ) doped-channel FET's (DCFET's) grown by GSMBE exhibiting excellent dc and microwave characteristics were successfully fabricated. A high  $g_m$  of 306 mS/mm, a high  $f_t$  of 21.7 GHz and a high  $f_{max}$  of 53.4 GHz were achieved at 300 K for a  $Ga_{0.51}In_{0.49}P/In_{0.2}Ga_{0.8}As$  DCFET with a 1 µm-long gate. This device also showed a very high maximum current density (630 mA/mm) and a very high drain-source operating voltage (13 V). These values were quite high compared with other works of InGaAs channel DCFET's and HEMT's with same gate length. Moreover, wide and flat characteristics of  $g_m$ ,  $f_t$  and  $f_{max}$  versus drain current (or gate voltage) were attained for all DCFET's. Power performance of  $Ga_{0.51}In_{0.49}P/In_{0.2}Ga_{0.8}As$  DCFET's,  $Al_{0.3}Ga_{0.7}As/In_{0.2}Ga_{0.8}As$  DCFET's and HEMT's were calculated. It is found that  $Ga_{0.51}In_{0.49}P/In_{0.2}Ga_{0.8}As$  DCFET's provides the largest power among the three devices. These results demonstrate that high transconductance, high linearity, high speed and high output-power could be achieved by using  $In_xGa_{1-x}As$  and  $Ga_{0.51}In_{0.49}P$  as the channel and insulator materials, respectively.

## I. Background

High electron mobility transistors (HEMT's) have demonstrated excellent performance in lownoise applications[1]. As for high-power applications, the heterostructure FET's (HFET's) based on an InGaAs pseudomorphic channel have shown extremely good power performance at millimeterwave frequencies due to high-current handling capability, high transconductance (g<sub>m</sub>), and good electron confinement by the potential well [2],[3]. It has been demonstrated that the current-drivability and gm of metal/i-AlGaAs/ n-InGaAs/i-GaAs quantum well MISFET's with doped InGaAs channel were higher than those of metal/i-AlGaAs/i-InGaAs/n-GaAs quantum well MISFET's with undoped InGaAs channel [3]. Therefore, we would like to study the performance of the metal/i-GaInP/n-InGaAs/i-GaAs dopedchannel FET's (DCFET's). There are several advantages by using the GaInP/InGaAs/GaAs material system compared with AlGaAs/InGaAs/ GaAs system: 1) the etching selectivity between Ga<sub>0.51</sub>In<sub>0.49</sub>P and GaAs is very high and therefore gate recess will stop at the undoped Ga<sub>0.51</sub>In<sub>0.49</sub>P layer automatically and exactly, which means high uniformity and yield [4]; 2) the reliability should be better since Ga<sub>0.51</sub>In<sub>0.49</sub>P has very low

reactivity with oxygen [4],[5]; and 3) the 1/f noise is lower due to smaller surface recombination [6]. Hence, in this paper, we report the peformance of the Ga<sub>0.51</sub>In<sub>0.49</sub>P/In<sub>x</sub>Ga<sub>1-x</sub>As/GaAs DCFET's and compared them with other works of InGaAs channel DCFET's and HEMT's.

#### II. Experimental Details

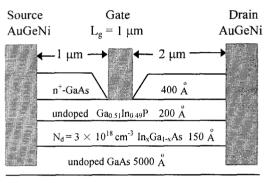

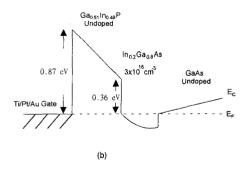

The Ga<sub>0.51</sub>In<sub>0.49</sub>P/In<sub>x</sub>Ga<sub>1-x</sub>As DCFET structure shown in Fig. 1(a) was grown by GSMBE. First, a 5000  $\overset{\circ}{A}$  undoped GaAs buffer layer was grown on a (100) GaAs semi-insulating substrate, followed by a 150  $^{\circ}_{A}$  In<sub>x</sub>Ga<sub>1-x</sub>As n channel layer  $(3 \times 10^{18}$  $\text{cm}^{\text{-}3}, \text{ Si doped}$  ). Then a 200  $\overset{\circ}{A}$  undoped Ga<sub>0.51</sub>In<sub>0.49</sub>P insulator layer was grown on top of the active channel. Finally, a 400 Å n+ GaAs cap layer was grown. Conventional optical lithography and mesa type wet etching technique were used to fabricate the Ga<sub>0.51</sub>In<sub>0.49</sub>P/In<sub>x</sub>Ga<sub>1-x</sub>As DCFET's [7]. After the GaAs cap layer was selectively etched, 1  $\mu$ m-long, 150  $\mu$ m-wide Ti/Pt/Au (500  $\overset{\circ}{A}$ /500  $\overset{\circ}{A}$ / 6000 Å) traditional gates were evaporated and defined by a lift-off process. The recess length between gate-drain and gate-source were 2 µm and 1 μm, respectively, as shown in Fig. 1(a). Fig. 1(b)

is the schematic conduction-band diagram of the  $Ga_{0.51}In_{0.49}P/In_{0.2}Ga_{0.8}As$  DCFET's. Because the gate is sitting directly on the *undoped* high bandgap  $Ga_{0.51}In_{0.49}P$  insulator layer (1.92 eV) with reasonably high Schottky barrier (0.87 eV) [8] and conduction band discontinuity at the  $Ga_{0.51}In_{0.49}P/In_{0.2}Ga_{0.8}As$  heterojunction is also large ( $\sim 0.36$  eV) [8],[9], higher gate turn on voltage, breakdown voltage and current drivability, as compared to MESFET's and HEMT's, can therefore be expected. The measured gate turn on voltage of  $Ga_{0.51}In_{0.49}P/In_{0.2}Ga_{0.8}As$  DCFET's was 1.05 eV. This value is comparable to that (1.0 eV) of  $Al_{0.3}Ga_{0.7}As/In_{0.2}Ga_{0.8}As$  DCFET's and better than that (0.65 eV) of  $Al_{0.3}Ga_{0.7}As/In_{0.2}Ga_{0.8}As$  HEMT's [10].

S.I. (100) GaAs substrate

(a)

Fig. 1(a) Device cross-section of  $Ga_{0.51}In_{0.49}P/In_xGa_{1-x}As$  DCFET's and (b) conduction band diagram of the  $Ga_{0.51}In_{0.49}P/In_{0.2}Ga_{0.8}As$  DCFET's.

## III. Results and Discussions

# A. DC Characteristics

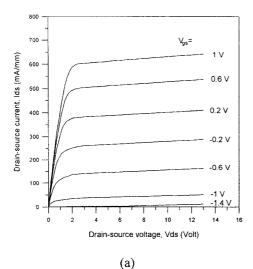

I-V characteristics of  $Ga_{0.51}In_{0.49}P/In_xGa_{1-x}As$  ( $0 \le x \le 0.22$ ) DCFET's were measured with an HP4156 precise semiconductor parameter analyzer. Typical drain-source current ( $I_{ds}$ ) versus drain-source voltage ( $V_{ds}$ ) characteristics of an

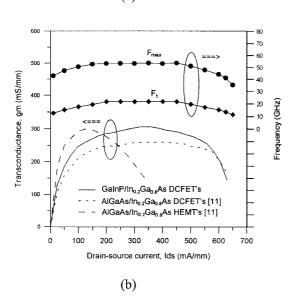

x=0.20 DCFET is shown in Fig. 2(a). Note that the device could be operated up to  $I_{ds} = 630$ mA/mm and  $V_{ds}=13$  V at  $V_{gs}=1$ V. This is attributed to the high-quality undoped highbandgap Ga<sub>0.51</sub>In<sub>0.49</sub>P insulator layer, which could sustain a very high breakdown field at the gate edge nearest to the drain. A peak gm of 306 mS/mm was also achieved at  $V_{ds} = 3$  V. The output conductance ( $g_{ds}$ ) at  $V_{gs}$ = 0 V was 2.1 mS/mm and therefore a high dc gain ratio (g<sub>m</sub>/g<sub>ds</sub>) of 147 was obtained. The I<sub>ds</sub> dependence of g<sub>m</sub> for  $Ga_{0.51}In_{0.49}P/In_{0.2}Ga_{0.8}As$ DCFET's Al<sub>0.3</sub>Ga<sub>0.7</sub>As/In<sub>0.2</sub>Ga<sub>0.8</sub>As DCFET's and HEMT's [11] were shown in Fig. 2(b). As can be seen clearly, the characteristics curve of g<sub>m</sub> versus I<sub>ds</sub>  $Ga_{0.51}In_{0.49}P/In_{0.2}Ga_{0.8}As$  DCFET's and Al<sub>0.3</sub>Ga<sub>0.7</sub>As/In<sub>0.2</sub>Ga<sub>0.8</sub>As DCFET's extended not only to higher I<sub>ds</sub> values but also exhibited flatter gm characteristics with wider drain bias current conditions, namely, 365 mA/mm for Ga<sub>0.51</sub>In<sub>0.49</sub>P /In<sub>0.2</sub>Ga<sub>0.8</sub>As DCFET's and 360 mA/mm for Al<sub>0.3</sub>Ga<sub>0.7</sub>As/In<sub>0.2</sub>Ga<sub>0.8</sub>As DCFET's in contrast with 150 mA/mm for Al<sub>0.3</sub>Ga<sub>0.7</sub>As/In<sub>0.2</sub>Ga<sub>0.8</sub>As HEMT's. The " width " of flat region was defined as the difference of two current densities corresponding to 10% drop from the maximum g<sub>m</sub>. The above results demonstrated that dopedchannel MIS-like structure indeed could achieve higher current drivability and better linearity [7],[11].

Due to the high etching selectivity between GaAs cap layer and Ga<sub>0.51</sub>In<sub>0.49</sub>P insulator layer, the standard deviation of the threshold voltage of our fabricated DCFET's was low to 50 mV. This value was comparable to that (60 mV) of GaInP/AlGaAs/InGaAs HJFET's fabricated by selective wet etching and less than one sixth of that of the conventional AlGaAs/InGaAs HJFET's [12], indicating great potential in using a highlyselective etching technique for high-uniformity and high-yield device production. Recent reports have shown that GaInP/GaAs devices guarantee a mean time to failure (MTTF) of 10<sup>8</sup> hours (at a junction temperature of 125 °C) [4] and at least 10<sup>6</sup> hours at a junction temperature of 200 °C [5], which is enough for a 25-year lifetime requirement of a practical system and suggests high reliability of GaInP/GaAs devices. From the above results, Ga<sub>0.51</sub>In<sub>0.49</sub>P/In<sub>x</sub>Ga<sub>1-x</sub>As material system should be a good alternate to AlGaAs/InGaAs system.

Table I summarizes the dc characteristics of  $Ga_{0.51}In_{0.49}P/In_xGa_{1-x}As$  ( $0 \le x \le 0.22$ ) DCFET's with 1.0 µm-long gate at room temperature. We observed an enhancement of  $g_{m,ext}$  from 180

Fig. 2(a) Typical  $I_{ds}$  v.s. $V_{ds}$  characteristics of the  $Ga_{0.51}In_{0.49}P/In_{0.2}Ga_{0.8}As$  DCFET and (b)  $g_m$ ,  $f_t$  and  $f_{max}$  v.s.  $I_{ds}$  characteristics of  $Ga_{0.51}In_{0.49}P/In_{0.2}Ga_{0.8}As$  DCFET's.

$\begin{array}{ccc} & Table\ I \\ DC\ characteristics\ of\ Ga_{0.51}In_{0.49}P/In_xGa_{1-x}As \\ (0\leq x\leq 0.22)\ DCFET's\ with\ 1.0\ \mu m\text{-long\ gate}. \end{array}$

| In content                   | x=0 | x=0.15 | x=0.20 | x=0.22 |

|------------------------------|-----|--------|--------|--------|

| g <sub>m,ext</sub> (mS/mm)   | 180 | 350    | 306    | 275    |

| I <sub>ds, max</sub> (mA/mm) | 465 | 575    | 630    | 585    |

mS/mm for x=0 - 350 mS/mm for x=0.15 DCFET's. However,  $g_{m,ext}$  values dropped to 306 mS/mm for x=0.20 and 275 mS/mm for x=0.22 DCFET's. The

optimum performance of  $Ga_{0.51}In_{0.49}P/In_xGa_{1-x}As$  DCFET's is obtained with the x value ranging between x=0.15 and x=0.20 for 150  $\mathring{A}$  thick  $In_xGa_{1-x}As$  channel layer and 200  $\mathring{A}$  thick  $Ga_{0.51}In_{0.49}P$  insulator layer.

## B. Microwave Characteristics

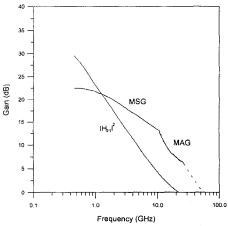

Microwave on wafer S-parameters, for 1.0 µmlong gate  $Ga_{0.51}In_{0.49}P/In_xGa_{1-x}As$  (0\le x\le 0.22) DCFET's were measured from 45 MHz to 26.5 GHz with an HP8510C network analyzer, Fig. 3 shows the current gain cut-off frequency (ft) and maximum oscillation frequency  $(f_{max})$  of x = 0.20In<sub>x</sub>Ga<sub>1-x</sub>As channel DCFET's were 21.7 and 53.4 GHz respectively under the bias conditions of  $V_{ds}$ = 3 V and  $V_{gs}$  = 0 V. The  $f_t$  (21.7 GHz) of Ga<sub>0.51</sub>In<sub>0.49</sub>P/In<sub>0.2</sub>Ga<sub>0.8</sub>As DCFET's was higher than those of Al<sub>0.3</sub>Ga<sub>0.7</sub>As/In<sub>0.2</sub>Ga<sub>0.8</sub>As DCFET's (12 GHz) and HEMT's 14.5 (GHz) with 1.0 µm-long gate [10]. Moreover, the  $f_{max}$  (53.4 GHz) of our Ga<sub>0.51</sub>In<sub>0.49</sub>P/In<sub>0.2</sub>Ga<sub>0.8</sub>As DCFET was comparable to those of Al<sub>0.3</sub>Ga<sub>0.7</sub>As/In<sub>0.2</sub>Ga<sub>0.8</sub>As DCFET's (50 GHz) and HEMT's (50 GHz) with 1.0 µm-long gate [10]. The higher f<sub>t</sub> performance of our  $Ga_{0.51}In_{0.49}P/In_{0.2}Ga_{0.8}As$ **DCFET** versus  $Al_{0.3}Ga_{0.7}As/In_{0.2}Ga_{0.8}As$  DCFET insulator thickness 200 Å ) was mainly attributed to higher g<sub>m</sub> due to higher mobility (3090 cm<sup>2</sup>/Vsec for our DCFET versus 1810 cm<sup>2</sup>/V-sec for  $Al_{0.3}Ga_{0.7}As/In_{0.2}Ga_{0.8}As$  DCFET) [10]. The mobility difference could be due to different growth techniques used. Though the mobility of our Ga<sub>0.51</sub>In<sub>0.49</sub>P/In<sub>0.2</sub>Ga<sub>0.8</sub>As DCFET was lower than that  $(3800 \text{ cm}^2/\text{V-sec})$  of  $Al_{0.3}Ga_{0.7}As$ /In<sub>0.2</sub>Ga<sub>0.8</sub>As HEMT, the g<sub>m</sub> of our DCFET's was still larger than its due to the higher product of mobility and sheet charge density. Moreover, the lower gate-source and gate-drain capacitances of our  $Ga_{0.51}In_{0.49}P/In_{0.2}Ga_{0.8}As$  DCFET (  $C_{gs} =$ 2023.2 fF/mm and  $C_{gd} = 157.8$  fF/mm versus  $C_{gs} =$ 3030 fF/mm and  $C_{gd} = 190$  fF/mm of  $Al_{0.3}Ga_{0.7}As$  $/In_{0.2}Ga_{0.8}As$  DCFET and  $C_{gs} = 2850$  fF/mm and  $C_{gd} = 250 \text{ fF/mm of } Al_{0.3}Ga_{0.7}As/In_{0.2}Ga_{0.8}As$ HEMT) also benefit the high  $f_t$  performance.

Table II summarizes the RF characteristics of the  $Ga_{0.51}In_{0.49}P/In_xGa_{1-x}As$  ( $0 \le x \le 0.22$ ) DCFET's with 1.0 µm-long gate at room temperature. The optimum performance of  $f_t$ 's and  $f_{max}$ 's both occured when the x value ranging between x = 0.15 and x = 0.20 for 150  $\mathring{A}$  thick  $In_xGa_{1-x}As$  channel layer and 200  $\mathring{A}$  thick  $Ga_{0.51}In_{0.49}P$  insulator layer.

Fig. 3 Microwave characteristics of Ga<sub>0.51</sub>In<sub>0.49</sub>P/In<sub>0.2</sub>Ga<sub>0.8</sub>As DCFET's with 1 µm-long gate.

Fig. 4 Power performance of  $Ga_{0.51}In_{0.49}P/In_{0.2}Ga_{0.8}As$  DCFET's,  $Al_{0.3}Ga_{0.7}As/In_{0.2}Ga_{0.8}As$  DCFET's and HEMT's at 2.4 GHz. (gate dimension:  $1\times100~\mu m^2$ )

Table II RF characteristics of  $Ga_{0.51}In_{0.49}P/In_xGa_{1-x}As$  (0 $\leq$ x $\leq$ 0.22) DCFET's with 1.0  $\mu$ m-long gate.

| In content             | x=0  | x=0.15 | x=0.20 | x=0.22 |

|------------------------|------|--------|--------|--------|

| f <sub>t</sub> (GHz)   | 17.6 | 23.3   | 21.7   | 19.1   |

| f <sub>max</sub> (GHz) | 34.9 | 50.8   | 53.4   | 46.8   |

## IV. Conclusions

In summary, the  $Ga_{0.51}In_{0.49}P/In_xGa_{1-x}As$  DCFET's ( $0 \le x \le 0.22$ ) grown by GSMBE were fabricated successfully and easily because of the high etching selectivity between  $Ga_{0.51}In_{0.49}P$  and GaAs. Due to superior transport properties of

$In_xGa_{1-x}As$  (0.15 $\le x\le 0.2$ ), high-quality *undoped* high bandgap  $Ga_{0.51}In_{0.49}P$  insulator layer, large Schottky barrier and  $Ga_{0.51}In_{0.49}P/In_xGa_{1-x}As$  conduction band-offset, high  $g_m$ , high current drivability, high operating voltage, high output-power and high-speed were achieved. Therefore,  $Ga_{0.51}In_{0.49}P/In_xGa_{1-x}As$  (0.15 $\le x\le 0.2$ ) DCFET's will be very promising candidates for microwave power application.

## Acknowledgement

Support from the National Science Council of R.O.C. under contract No. NSC86-2221-E-002-046 is acknowledged.

### References

- [1] K. L. Tan, R. M. Dia, Dwight C. Streit, A. C. Han, Tien Q. Trinh, J. R. Velebir, P. H. Liu, Tzvenshyan Lin, H. C. Yen, M. Sholley and L. Shaw, *IEEE Electron Device Lett.*, vol. 11, no. 7, pp. 303-305, 1990.

- [2] P. Saunier, R. J. Matyi and Bradshaw, *IEEE Electron Device Lett.*, vol. 9, no. 8, pp. 397-398, 1988.

- [3] B. Kim, R. J. Matyi, M. Wurtele, K. Bradshaw, M. A. Khatibzadeh and H. Q. Tserng, *Electron Devices*, vol. 36, no. 10, pp. 2236-2242, 1989.

- [4] Herman Willemsen and David Nicholson, *IEEE GaAs IC Symp. Tech. Dig.*, 1996, pp. 10-13.

- [5] T. Ihara, Y. Oikawa, T. Yamamoto, H. Tomofuji, H. Hamaro, H. Ohnishi and Y. Watanabo, *IEEE GaAs IC Symp. Tech. Dig.*, 1996, pp. 262-265.

- [6] A. Ginoudi, E. Paloura, G. Costandinidis, J. Ch. Garcia and Ph. Maurel, *Proc. 4th Int. Conf. InP and Related Mater.*, 1992, pp. 389-392.

- [7] Y. S. Lin, S. S. Lu and T. P. Sun, *IEEE Electron Device Lett.*, vol. 16, no. 11, pp. 518-520, 1995.

- [8] Y. J. Chan, D. Pavlidis, M. Razeghi and F. Omnes, *IEEE Trans. Electron Device.*, vol. 37, pp. 2141-2147, 1990.

- [9] A. W. Hanson, S. A. Stockman and G. E. Stillman, *IEEE Electron Device Lett.*, vol. 14, no. 1, pp. 25-29, 1993.

- [10] M. T. Yang and Y. J. Chan, *IEEE IEEE Electron Devices*, vol. 43, no. 8, pp. 1174-1179, 1996.

- [11] Y. J. Chan and M. T. Yang, *IEEE Electron Device Lett.*, vol. 16, no. 1, pp. 33-35, 1995.

- [12] Y. Okamoto, K. Matsunaga and M. Kuzuhara, *Electron. Lett*, vol. 31, no. 25, pp. 2216-2217, 1995.