## Partitioned gate tunnelling current model considering distributed effect for CMOS devices with ultra-thin (1 nm) gate oxide

## C.H. Lin, J.B. Kuo, K.W. Su and S. Liu

The partitioned gate tunnelling current model considering the distributed effect for CMOS devices with an ultra-thin (1 nm) gate oxide is reported. As verified by the experimentally measured data, the partitioned gate tunnelling current model considering the distributed effect provides a better prediction of the total gate, drain and source currents as compared to the BSIM4 model.

Introduction: Gate leakage current due to tunnelling through the gate oxide has become a serious phenomenon for advanced CMOS devices with an ultra-thin gate oxide [1]. The impacts of the gate tunnelling current on the performance of the circuits using nanometre CMOS devices with an ultra-thin gate oxide cannot be neglected [2]. In fact, the gate tunnelling current is distributed along the channel, which makes the gate tunnelling current difficult to model. For good assessment of the influence of the gate tunnelling current, an accurate gate tunnelling current model is required. In this Letter, following a double integral approach as for deriving the partitioned-charge model [3], the partitioned gate tunnelling current model considering the distributed effect is reported. It is shown that, as verified by the experimentally measured data, the partitioned gate tunnelling current model considering the distributed effect provides a better prediction of the total gate, drain and source currents as compared to the BSIM4 model.

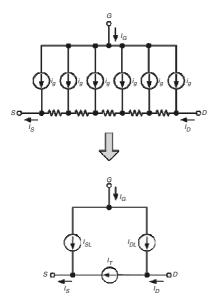

Fig. 1 Distributed and partitioned gate tunnelling current models

*Partitioned*  $I_G$  model: Fig. 1*a* shows the distributed gate tunnelling current model. Depending on the location in the lateral channel, the local gate tunnelling current varies. Considering the distributed tunnelling current, the total gate current is divided into the source-side component ( $I_{SL}$ ) and the drain-side one ( $I_{DL}$ ) in the partitioned gate tunnelling current model, as shown in Fig. 1*b*. Following the approach for deriving the partitioned charge model for MOS transistors [3], the total gate tunnelling current is expressed as  $I_G = W/L \int_0^L \int_0^L J_0^L O_G(y) dy dy$ , where  $J_G(y) = J_{GO}e^{-B^*V(y)}$  [4] is the local gate tunnelling current density location at location *y* in the lateral channel, and  $B^*$  is a fitting parameter with a nonzero value. From the above equations with the channel drift current, the total gate tunnelling current is:

$$I_{G} = \frac{J_{G0}WL}{B^{*}[(V_{G} - V_{T})V_{DS} - (m/2)V_{DS}^{2}]} \times \left\{ V_{G} - V_{T} - \frac{m}{B^{*}} + e^{-B^{*}V_{DS}} \left[ mV_{DS} - (V_{G} - V_{T}) + \frac{m}{B^{*}} \right] \right\}$$

where  $J_{G0}$  is the  $J_G$  at  $V_{DS} = 0$  V, and *m* is a fitting parameter with a nonzero value. Similarly, the drain component of the gate tunnelling current is expressed as  $I_{DL} = W/L \int_0^L \int_y^L J_G(y) dy dy$ , which could be simplified using integral by parts as:

Thus

$$\begin{split} I_{DL} &= \frac{J_{G0}WL}{B^*[(V_G - V_T)V_{DS} - (m/2)V_{DS}^2]^2} \\ &\times \left\{ \frac{1}{B^*}(V_G - V_T)^2 \\ &- \frac{3m}{B^{*2}}(V_G - V_T) + \frac{3m^2}{B^{*3}} + e^{-B^*V_{DS}} \left\{ -\frac{m^2}{2}V_{DS}^3 \\ &+ \left[ \frac{3m}{2}(V_G - V_T) - \frac{3m^2}{2B^*} \right] V_{DS}^2 \\ &+ \left[ -(V_G - V_T)^2 + \frac{3m}{B^*}(V_G - V_T) - \frac{3m^2}{B^{*2}} \right] V_{DS} \\ &- \frac{1}{B^*}(V_G - V_T)^2 + \frac{3m}{B^{*2}}(V_G - V_T) - \frac{3m^2}{B^{*3}} \right\} \end{split}$$

and the source component of the gate tunnelling current is:

$$I_{SL} = \frac{W}{L} \int_0^L \int_0^y J_G(y) dy \, dy$$

$$\begin{split} I_{SL} &= \frac{J_{G0}WL}{B^*[(V_G - V_T)V_{DS} - (m/2)V_{DS}^2]^2} \\ &\times \left\{ -\frac{1}{B^*}(V_G - V_T)^2 + \frac{3m}{B^{*2}}(V_G - V_T) - \frac{3m^2}{B^{*3}} \right. \\ &+ \left( V_G - V_T - \frac{m}{B^*} \right) \left( V_G - V_T - \frac{m}{2}V_{DS} \right) V_{DS} \\ &+ e^{-B^*V_{DS}} \left[ \frac{1}{B^*}(V_G - V_T)^2 - \frac{3m}{B^{*2}}(V_G - V_T) \\ &+ \frac{3m^2}{B^{*3}} + \frac{3m^2}{B^{*2}}V_{DS} - \frac{2m}{B^*}(V_G - V_T)V_{DS} + \frac{m^2}{B^*}V_{DS}^2 \right] \end{split}$$

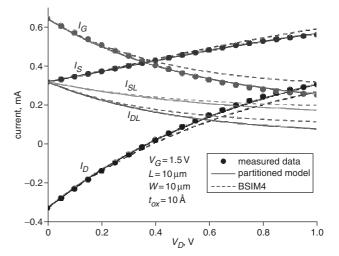

Fig. 2 Total gate tunnelling current ( $I_G$ ), partitioned gate tunnelling currents ( $I_{SL}$ ,  $I_{DL}$ ), total drain current ( $I_D$ ), and total source current ( $I_S$ ) against drain voltage of NMOS device with 1 nm gate oxide and aspect ratio of 10 µm/10 µm biased at gate voltage of 1.5 V, based on experimentally measured data (dots), BSIM4 (dashed lines) and partitioned model result (solid lines)

Model evaluation and discussion: To assess the effectiveness of this partitioned gate tunnelling current model, the model results have been compared with the experimentally measured data of a test NMOS device with an ultra-thin gate oxide of 1 nm and an aspect ratio of 10  $\mu$ m/10  $\mu$ m. Fig. 2 shows the total gate tunnelling current ( $I_G$ ), the partitioned gate tunnelling currents ( $I_{SL}$ ,  $I_{DL}$ ), the total drain current ( $I_D$ ), and the total source current ( $I_S$ ) against the drain voltage of the NMOS test device, biased at a gate voltage of 1.5 V, based on the experimentally measured data (dots) and the partitioned model result (solid lines). Also shown in the Figure is the result based on the BSIM4 model (dashed lines) [5]. As shown in the Figure, as verified by the experimentally measured data, the partitioned gate tunnelling current model could provide a more accurate prediction of  $I_G$ ,  $I_S$ ,  $I_D$ ,

ELECTRONICS LETTERS 2nd February 2006 Vol. 42 No. 3

$I_{SL}$ , and  $I_{DL}$  as compared to the BSIM4 model [5]. In addition, at a higher  $V_D$  the effectiveness of the partitioned charge model is higher.

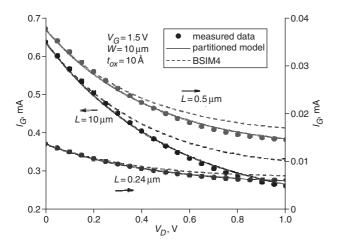

**Fig. 3** Total gate tunnelling current  $(I_G)$  against drain voltage of NMOS device with 1 nm gate oxide, channel width of 10 µm, and various channel lengths of 10, 0.5 and 0.24 µm, biased at gate voltage of 1.5 V, based on experimentally measured data (dots), BSIM4 (dashed lines) and partitioned model result (solid lines)

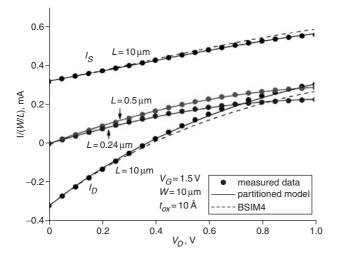

**Fig. 4** Total drain current  $(I_D)$  and total source current  $(I_S)$  against gate voltage of NMOS device with 1 nm gate oxide, a channel width of 10 µm, and various channel lengths of 10, 0.5 and 0.24 µm, biased at gate voltage of 1.5 V, based on experimentally measured data (dots), BSIM4 (dashed lines) and partitioned gate tunnelling current model result (solid lines)

Fig. 3 shows the total gate tunnelling current  $(I_G)$  and the total source/drain current  $(I_S/I_D)$  against the drain voltage of the NMOS test device with a 1 nm gate oxide, a channel width of 10 µm, and various channel lengths of 10, 0.5 and 0.24 µm, biased at a gate voltage of 1.5 V, based on the experimentally measured data (dots), BSIM4 (dashed lines) and the partitioned model result (solid lines). Fig. 4 shows the total drain current  $(I_D)$  and the total source current  $(I_S)$ against the drain voltage of the NMOS device with a 1 nm gate oxide, a channel width of 10  $\mu$ m, and various channel lengths of 10, 0.5 and  $0.24\,\mu\text{m},$  biased at a gate voltage of 1.5 V, based on the experimentally measured data (dots), BSIM4 (dashed lines) and the partitioned gate tunnelling current model result (solid lines). As shown in the Figures, the partitioned charge model could provide a better prediction of the current behaviour as verified by the experimentally measured data while compared to the BSIM4 model [5]. Its effectiveness is greater at a higher  $V_D$ .

© IEE 2006 *Electronics Letters* online no: 20064060 doi: 10.1049/el:20064060

C.H. Lin and J.B. Kuo (Department of Electrical Engineering, National Taiwan University, Taipei, Taiwan 10617, Republic of China)

20 November 2005

E-mail: jbkuo888@yahoo.ca

K.W. Su and S. Liu (TSMC, Hsinchu, Taiwan 300, Republic of China)

## References

- Timp, G., *et al.*: 'Low leakage, ultra-thin gate oxides for extremely high performance sub-100 nm nMOSFETs'. IEDM Dig., December 1997, pp. 930–932

- 2 Choi, C.H., Nam, K.Y., and Dutton, R.W.: 'Impact of gate direct tunneling current on circuit performance', *IEEE Trans. Electron. Devices*, 2001, **48**, (12), pp. 2823–2829

- 3 Ward, D.E., and Dutton, R.W.: 'A charge-oriented model for MOS transistor capacitances', *IEEE J. Solid-State Circuits*, 1978, **13**, (5), pp. 703–708

- 4 Schuegraf, K.F., and Hu, C.: 'Hole injection SiO<sub>2</sub> breakdown model for very low voltage lifetime extrapolation', *IEEE Trans. Electron. Devices*, 1994, **41**, (5), pp. 761–767

- 5 Lee, W., and Hu, C.: 'Modeling CMOS tunneling currents through ultrathin gate oxide due to conduction- and valence-band electron and hole tunneling', *IEEE Trans. Electron. Devices*, 2001, **48**, (7), pp. 1366–1373